基于FPGA 的SiP 原型验证平台设计

杨楚玮,张梅娟,侯庆庆

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

随着电子整机系统小型化、高性能、多功能、高可靠和低成本要求越来越高[1-2],在保证系统可靠性的前提下,最大程度提高系统的集成度势在必行。系统级封装技术可将不同工艺类型、不同功能的电子元器件集成到一个电子系统中[3],能够满足电子整机系统发展的需求,在军用电子系统中得到了广泛的应用。

目前整机系统是在PCB 板级上使用多个芯片进行组合,SiP 是对裸片直接进行封装,将多个裸芯集成在一个腔体内[4]。该技术减少了系统面积,与PCB 板级相比缩短了芯片间的连线,降低了走线的延迟和寄生效应,使得信号传输更加可靠[5]。同时,多个裸芯的集成减少了器件的重量和器件的引脚数,降低了硬件设计的风险。SiP 不仅可以集成不同工艺类型的芯片,实现混合信号的集成;而且减少了封装的工序,相应地降低了生产制造成本,缩短了产品的研发周期。

本文使用ADC+SoC+DAC 架构设计一款基于FPGA的SiP 原型验证平台,SoC 内部集成了可重构算法单元,通过软硬件协同验证,查找SoC 设计中是否存在缺陷,弥补了仿真验证效率和速度低下的问题,增加了芯片验证的覆盖率,保证了设计的可靠性和正确性[6-7]。同时,验证了该架构进行SiP 封装设计的可行性[8]。

1 系统架构

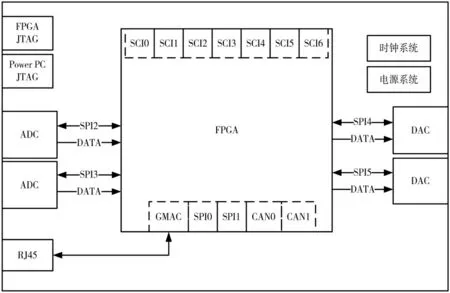

本文验证原型为基于FPGA 平台搭建的ADC+SoC+DAC 架构的SiP,其中SiP 内部集成2 片4 通道16 位的ADC、2 片2 通道16 位的DAC 和1 片SoC,SiP内部结 构如图1 所示。SoC 使用IBM PowerPC470 作为主控处理器[9],以AHB 总线为数据链路,内部集成资源包括:(1)SCI、SPI、CAN、GPIO、GMAC 等通用外设模块;(2)可重构算法单元(可重构IP);(3)ROM、Flash、SRAM 等存储设备。整个SiP 的硬件资源组成如表1 所示。

表1 硬件资源结构

图1 SiP 内部结构框图

可重构IP 搭载到处理器的AHB 总线上,处理器可通过AHB 总线对可重构IP 进行配置和读写控制。可重构IP 由串行数字下变频模块、重构阵列、相关解扩模块、识别模块、DPSK/PPM 解调模块、配置总线等组成。ADC采集的数据经可重构IP 处理后,由DAC 输出对应的响应信号。重构IP 结构示意如图2 所示。

图2 重构IP 结构示意图

FPGA 作为SoC 验证的载体,将SoC 的ASIC 代码移植到FPGA 上,模拟SoC 的实际运行环境,ADC 和DAC为SiP 内部的裸芯封装的电路,保证了原型验证平台的环境与SiP 内部的一致性[10]。

2 原型验证平台

本文设计的FPGA 原型验证平台用于验证SoC 的功能实现和SiP 架构的可行性。该验证平台选用的FPGA器件型号为XCVU440-FLGA2892-1-C,能够满足该型号SoC 逻辑的需求,详细可编程参数如表2 所示。选用的ADC 和DAC 芯片为SiP 中裸芯封装的器件。FPGA 原型验证平台结构如图3 所示,时钟模块为FPGA、ADC 和DAC提供时钟,串口SCI 与PC 串口连接进行通信,GMAC通过RJ45 接口与PC 网口通信[11],SPI 接口实现ADC 和DAC的相关参数配置[12],CAN 和SPI 与包含对应接口功能的工具进行通信。

图3 FPGA 原型验证平台结构示意图

表2 FPGA 可编程参数

为验证SoC 的可重构IP,MATLAB 生产的数据文件经信号源转换为模拟信号,ADC 完成信号的采样,转换为数字信号,由SoC 的可重构算法单元进行梳理,信号识别正确后,发送对应的响应,经DAC 转成模拟信号,用示波器查看DAC 输出波形是否正确。整个处理过程PC 可进行实时监控,可通过串口或SPI 口对SoC 进行信息的交互,监控可重构算法处理情况。

3 软硬件协同验证

通用验证SiP 架构和SoC 功能的方法是通过将ASIC代码移植到FPGA,并通过对FPGA 搭建相关验证环境,进行SiP 系统级验证和SoC 功能验证[13]。

3.1 FPGA 移植

在FPGA 的原型验证中,FPGA 作为芯片验证的主要载体,将ASIC 代码移植到FPGA 上主要有三点优势:(1)能够有效提高整个电路的运行频率,缩短仿真时间;(2)运行真实的外围电路环境;(3)运行各类应用场景的软件。从而达到模拟芯片实际运行的目的。

由于ASIC 结构与FPGA 结构不同,ASIC 代码到FPGA的移植需要进行部分替换,主要集中在时钟、Memory 和IO。时钟需满足时序的要求,PLL 时钟结构与ASIC 保持一致,为保证可重构IP 的速率要求,需降低CPU 的速率;ASIC 中一般由工艺商提供的库或者Memory Complier 定制生成,需要转换成FPGA 内部对应的Memory 单元[14];ASIC 的Pad 使用的是ASIC 器件库中的单元,需要替换成FPGA 的I/O。完成ASIC 代码在FPGA 平台上替换后,在FPGA 上进行仿真,验证子模块功能,然后生成网表文件在硬件平台上进行验证[15]。

3.2 FPGA 验证系统

FPGA 验证系统是基于FPGA、软件、硬件构建的芯片验证平台,其主要目的是为了在设计阶段模拟芯片的实际运行环境,检测芯片的实际运行状态和实现功能是否与设计预期一致。本文提出的SiP 原型验证系统能够满足SiP 芯片软件和硬件测试需求,其系统结构如图4 所示。硬件主要包括FPGA 测试板卡、bit 文件下载器、软件调试仿真器、PC、信号源、示波器。软件主要包括Eclipse软件调试、confpro 下载软件、Wireshark、SecureCRT。

图4 FPGA 原型验证系统结构图

FPGA 软硬件验证步骤如下[16]:

(1)通过Xilinx 软件工具对待验SiP 系统进行综合和布局布线,生成bit 文件。

(2)通过confpro 下载软件将bit 文件下载到FPGA 测试板卡。

(3)软件相关调试通过Eclipse 和仿真器进行测试。

(4)裸机IP 验证则在系统内测试设计的各模块验证用例。

(5)可重构IP 则需要加入相应的用户算法进行测试。

在FPGA 平台验证SiP 系统过程中,裸机IP 的验证根据前端设计手册开发验证用例,通过测试设备和上位机测试软件来保证各模块功能的正确性,通过和其他接口的通信来验证模块的稳定性和获取模块性能参数。可重构IP 的验证根据用户算法开发验证用例,通过和测试仪器的交互确认用户算法功能的实现及正确性。系统验证流程如图5 所示。

图5 SiP 系统验证流程图

3.3 SiP 系统功能验证

SiP 系统功能验证包括两部分:(1)对裸机IP 进行验证,该过程前期用于定位和排查FPGA 软件设计和硬件板卡存在的问题,保证其稳定性和正确性,后期验证CPU和各模块功能;(2)对加入用户算法的可重构IP 进行验证,测试用户算法实现的正确性和稳定性。原型验证场景如图6 所示。

图6 原型验证场景图

3.3.1 裸机IP 验证

裸机IP 进行验证分为BootLoader 和外设模块验证。外设包括SCI、SPI、CAN、GPIO、GMAC。

BootLoader 不仅能够增加系统启动方式的种类,而且解决了系统内部存储空间过小的问题,扩充了系统外部存储资源。

BootLoader 验证包括以下步骤:

(1)FPGA 板上电复位,进行CPU 的初始化配置。

(2)读取Flash 用户配置区,判断信息是否有效。

(3)若有效,BootLoader 软件将Flash 用户代码区的代码搬移到RAM 中。当用户代码有效时,运行用户代码;当用户代码无效时,进入串口下载模式。

(4)若无效,进入串口下载模式。

(5)串口下载模式下,BootLoader 软件配置UART 接口,在口令输入正确后接收串口命令,执行相关操作。

BootLoader 验证流程如图7 所示。

图7 BootLoader 验证流程图

外设IP 的验证主要采取JTAG 在线Debug 和自动化测试两种方式。前期验证,通过在线Debug 进行覆盖性功能测试,根据外设IP 数据手册制定验证用例,确保设计功能的完整性和正确性。后期验证,在覆盖性测试通过的前提下,进行自动化测试,覆盖基础和重要功能,并进行集成测试和性能测试。

通用接口SCI、SPI、CAN、GPIO 外设硬件上通过连接通用接口转USB 工具USB2XXX 连接至上位机。在配套的上位机软件界面,显示接收的下位机外设IP 接口传输数据,并控制上位机传输数据至下位机外设IP 接口。

千兆网口GMAC 硬件上使用的PHY 芯片为88E1111,支持10/100/1 000 Mb/s 工作模式,支持GMII、MII、SGMII接口,通过RJ45 接口与外部互联完成数据传输。上位机通过抓包软件抓取下位机网口发送数据,通过发包软件发送数据包到下位机网口。测试内容包含:数据链路层和物理层功能测试,即网络控制器和PHY 层测试;在下位机工程中添加网络协议栈LWIP,进行网络层和应用层测试。

3.3.2 可重构IP 验证

可重构IP 验证的目的是为了测试该IP 在整个SiP中功能实现的正确性和稳定性。主要内容包括对IP 包括的前端滤波、解调、模式识别和模式发送四个模块实现功能进行验证。

测试包括5 个步骤:SiP 资源的初始化;MATLAB 生成激励文件,通过信号源产生测试激励;ADC 采样输入的激励,送至可重构IP;可重构IP 进行数据解析;输出响应到DAC,DAC 转换后输出到示波器。

可重构IP 的验证过程如下:

(1)在系统上电后,运行CPU 内部Flash 程序,对CPU、可重构IP 模块以及SPI、串口、时钟、ADC/DAC 等外设进行初始化。

(2)通过MATLAB 根据模式参数生成算法输入的测试激励文件,用信号源导入该文件,输出对应的信号。示例信号为300 MHz 载波上面包含DS 码值的20 MHz 正弦信号,如图8 所示,左边为整体波形图,右边为局部放大波形图。

图8 ADC 输入波形图

(3)信号源输出的信号加在ADC 的模拟输入端。ADC数字输出端的串行数字信号,经RXTOP 转换为并行的数据,输入到可重构IP 模块。

(4)可重构IP 的SDDC 模块对数据进行解析,提取DS 值,对提取的DS 码和初始化配置的DS 码进行比较,若相同,则CORR 模块生成相关峰,同时计算相关峰之间的间距信息,根据间距信息输出对应的响应信号到DAC。

(5)DAC 把响应信号转换成模拟信号输出。通过示波器查看输出的模拟信号,如图9 所示,左边为整体波形图,右边为局部放大波形图。

图9 DAC 输出波形图

4 结论

随着SiP 集成技术日趋成熟和ADC/DAC 转换器高精度、低功耗性能需求的提高,设计一款内含ADC和DAC 模块的SiP 芯片能够达到两者相容、互补长短的效果。

本文基于FPGA 硬件平台搭建了ADC+SoC+DAC架构的SiP 原型验证电路。该技术融合了SoC 对外围ADC/DAC 配套电路的配置接口和处理其信号的可重构算法,很大程度提高参数的可配置性和处理可重构性,增加了ADC/DAC 使用的灵活性。同时,硬件层面上减小了系统体积,降低了走线延迟和寄生效应,使得信号传输更加可靠[17]。测试结果证明了该架构SiP系统设计的可行性与正确性,为未来该类器件SiP 封装提供了设计思路和验证方案。