16Gbit/s 高速串并收发器调试及交流耦合电容选取方案

张秀均,于 治,宋林峰,季振凯

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

随着高速数据传输技术的快速发展,国际上高速串并收发器(SerDes)的传输速率可达56 Gbit/s 乃至112 Gbit/s,如何改善高速SerDes 的传输性能已成为研究的热点问题[1]。由于测试条件的限制,目前国内高速SerDes 的传输测试速率大多在10.3125 Gbit/s。为了保证信号的传输质量,AC 耦合电容广泛应用于高速SerDes 传输[2],因为AC 耦合电容能够消除收发模块间共模电压的失配,实现不同电压逻辑信号间的互连。耦合电容选取不当会造成码型抖动、信号传输质量恶化、误码率增加等。因此AC 耦合电容的选取对高速SerDes 传输至关重要。

相较于国外V7 系列12.5 Gbit/s 的SerDes 芯片,本研究基于公司研发的集成16 Gbit/s 高速SerDes 的FPGA 芯片,测试了不同速率下的SerDes 性能。基于可测性设计(DFT)[3]测试了不同速率下的眼图、抖动等性能参数,并通过理论分析和实际测试比较出不同速率下性能最好的AC 耦合电容值。

2 基于DFT 的高速SerDes 调试方法

2.1 高速SerDes 结构及参数

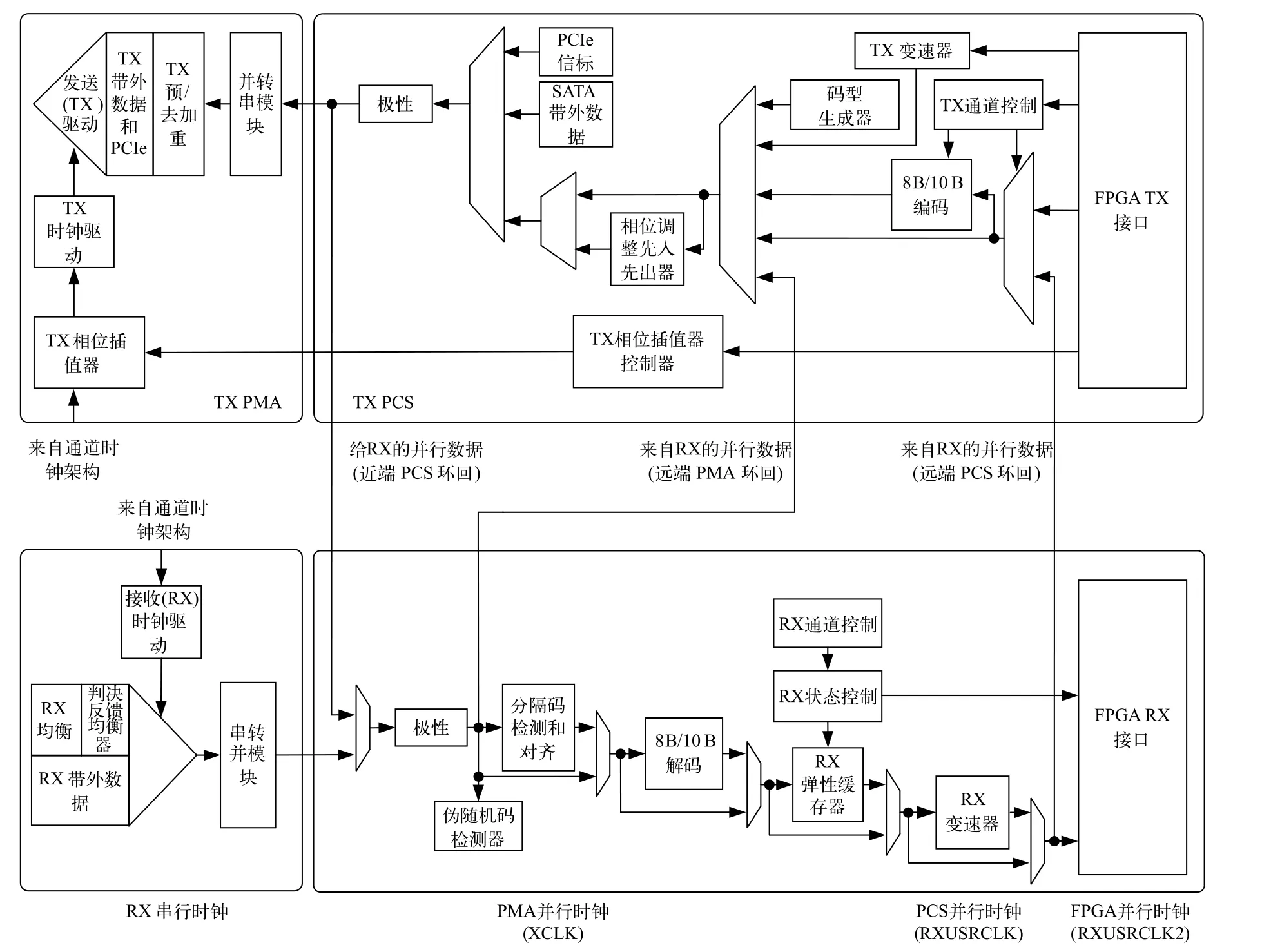

高速SerDes 由发送单元和接收单元组成,发端和收端的功能彼此相互独立且都包含物理媒介适配层(PMA)和物理编码子层(PCS)[4],高速SerDes 电路结构如图1 所示。

图1 高速SerDes 电路结构

高速SerDes 的功能本质上是实现串并转换,发送端将并行信号经过8 B/10 B 编码转化为串行信号后经过信道传输再解码为并行信号处理[5]。为了保证数据在高速传输过程中的稳定性,发送端和接收端还包含加重/预加重、时钟驱动、均衡、时钟恢复等模块,每个模块都有自己对应的参数配置。如何配置各模块的参数在高速SerDes 调试过程中至关重要,经统计,SerDes 调试过程中需要修改的配置参数达上百个。

2.2 JTAG 边界扫描原理

联合测试工作组(JTAG)[6]是一种由国际统一标准认证的芯片内部DFT 测试协议。边界扫描是JTAG的常见应用,通常情况下,高速SerDes 测试采用JTAG 进行配置。通过控制内部状态机的TMS 输入接口、控制时钟的TCK 控制接口、控制传输数据的TDI输入接口以及数据输出的TDO 接口下载SerDes 信息。

2.3 DFT 调试原理

除了JTAG 外,本研究在高速SerDes 调试过程中,还利用集成误码率测试仪(IBERT)协助测试。IBERT是Xilinx 提供的用于调试FPGA 芯片内高速串行接口比特误码率性能的工具,专用调试软件Vivado进行协议和时钟配置,生成用例后可以查看全部的配置参数。利用IBERT 进行高速SerDes 传输时,生成的二进制比特流通过光模块(SFP)收发器通道的发送(TX)端发送到FPGA 测试板的接收(RX)端,经过FPGA 内部功能模块后再由测试板TX 端返回输出到SFP RX 端。此外,在数据传输过程中还可以动态配置码型、摆幅、加重、环回模式等参数[7],给硬件调试带来很大的便利。

为了在调试过程中动态配置SerDes 参数,设计了16 Gbit/s SerDes 参数调试工具对寄存器进行读写,调试软件界面如图2 所示。其不仅可以导入配置程序对所有SerDes 参数进行全局读写,还可以针对特定通道对单个SerDes 参数进行动态读写,避免了全局读写造成的基础配置反复初始化,给调试带来很大便利。

图2 16 Gbit/s SerDes 参数调试软件界面

3 AC 耦合电容的选取方案

在进行高速SerDes 传输时,经常要使用AC 耦合电容保证信号的传输质量,常见的电容选取值是100nF和10 nF。电容值过大或过小都会增加直流压降并引起码型相关抖动,增加误码率。

3.1 直流压降

在高速SerDes 传输系统中,AC 耦合电容会引起阻抗变化,造成码型相关抖动。发送的伪随机码(PRBS)出现连续的0 或1 时,会出现直流压降,并且这个压降与时间常数RC 有关。其理论表达式为:

式中,R、C 分别代表终端电阻与AC 耦合电容,电容值越大,直流压降越小,VPP代表峰值电压。由于安装后的电容并不是理想的电容,除了等效串联电感和等效串联电阻外还安装有电感,存在串联谐振频率。电容在串联谐振频率前呈容性,之后呈感性,并且电容取值越大,谐振频率越小,造成高频分量衰减增大,误码率增加。

3.2 码型相关抖动

AC 耦合电容引起的码型相关抖动如图3 所示。图3 中,实线Diff(Pf)的P 端和N 端分别代表不归零编码(NRZ)的长“1”码型和长“0”码型的理想电压波形。当NRZ 翻转时,由于直流压降的存在,长“1”码型的实际电压波形翻转位置低于理想电压波形,见图中实线Diff(Ps)。因此,实际电压波形比理想电压更早达到共模电压水平,图中用Ts和Tf分别代表实际电压波形和理想电压波形到达共模电压的时间,二者的差值即表示为码型相关抖动(PDJ)[8],记为PDJ。

图3 AC 耦合电容引起的码型相关抖动

为了计算PDJ,需要测量信号电压值从20%上升到80%所用的时间,上升时间或下降时间定义为数据信号由低电平到高电平或从高电平到低电平转换的时间的平均值。假定上升沿斜率等于下降沿斜率,由图3可知,上升沿斜率表示为0.6 VPP/tr,下降沿斜率表示为ΔV/PDJ,因此可以得到:

联立式(1)(2)可以得到:

其中,tr≈0.26/BW,信号带宽BW可以近似等价为NRZ速率,终端电阻R 的值为50 Ω,C 为AC 耦合电容值,t表示长0 或长1 码保持的时间[9]。由式(3)可知,RC 时间常数越大,PDJ的值越大。

根据直流压降和码型相关抖动推导AC 耦合电容取值范围,假定高速SerDes 直流压降不超过电压摆幅的6%,即

式中,t=NUM×Tc,其中Tc表示每比特位的数据周期,NUM为最大连续0 或连续1 的数目。对式(4)进行推导即可得到AC 耦合电容值的最小值[10]:

本设计中假定NUM=32,根据式(3)(5)可以得到高速SerDes 典型速率下AC 耦合电容的最小取值及PDJ,当速率为16 Gbit/s 时,AC 耦合电容的理论最小取值为0.32 nF,为实验部分的耦合电容选取提供了理论依据。

4 试验验证

为了验证AC 耦合电容对高速SerDes 传输的影响,对本公司研发的16 Gbit/s 高速SerDes 的FPGA 芯片进行测试。测试内容包括高速SerDes 无源特性测试及SerDes 远端PMA 测试,通过分析接收眼图的眼高、眼宽及抖动来评估不同速率下AC 耦合电容的优劣。

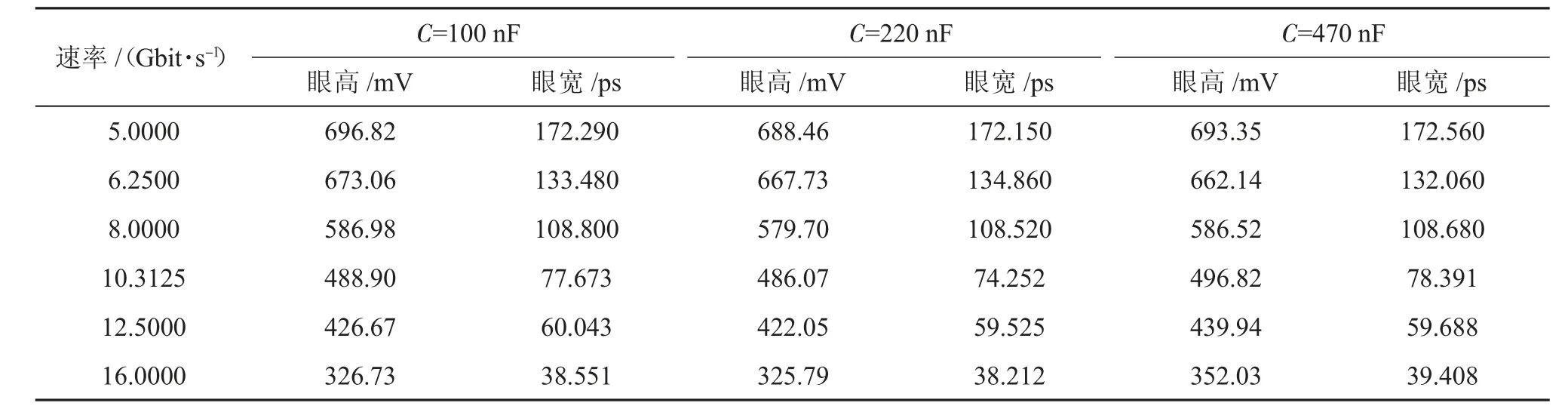

4.1 高速SerDes 无源特性测试

高速SerDes 的无源特性测试是将FPGA 测试板的TX 端传输到示波器进行眼图分析,通过IBERT 加载并动态配置SerDes 参数,码型选择PRBS31,环回模式设置为近端PMA 模式。分别使用100nF、220nF、470nF的电容作为AC 耦合电容,由于传输过程未注入抖动,接收端误码率为零,通过观测眼图的眼高和眼宽来选取合适的AC 耦合电容。表1 列出了高速SerDes 常见速率下测得的眼高和眼宽。从表1 可以发现,在速率小于10.3125 Gbit/s 时,使用100 nF 的耦合电容有更大的眼高和眼宽;而当速率大于10.3125 Gbit/s 时,使用470 nF 的耦合电容效果更好。根据第3 节的推论,选取100 nF 和470 nF 的耦合电容是完全可行的。

表1 高速SerDes 无源特性测试结果

4.2 高速SerDes 远端PMA 测试

高速SerDes 远端PMA 测试通过Keysight N4903B 误码仪和Xilinx ZCU111 开发板发送PRBS码到高速SerDes 验证板的RX 端。PC 端通过寄存器读写软件对指令列表中的参数进行配置,SerDes 结构与2.1 节给出的一致。动态配置的主要参数包括时钟选择、分频设置、环回模式、TX 摆幅、均衡模式、RX 共模电压选择等。使用JTAG 下载器加载配置到FPGA芯片,芯片发出的数据经过验证板的TX 端连接到示波器。

分别使用470 pF、10 nF、100 nF、470 nF 和680 nF的电容作为AC 耦合电容,发送码型设置为PRBS31,误码仪注入0.5 UI 的抖动产生误码,通过观测接收眼图的眼高和眼宽来评估耦合电容对传输的影响,误码率通过TJ 抖动呈现,抖动越大,误码率越高。试验结果见表2~4。

表2 高速SerDes 接收眼图眼高

表3 高速SerDes 接收眼图眼宽

表4 高速SerDes 传输TJ 抖动

对比表2 的结果可以发现,高速SerDes 远端PMA 测试结果与无源特性测试有相同的特点,都是在速率为10.3125 Gbit/s 以下时100 nF 的耦合电容有更大的眼高,10.3125 Gbit/s 以上时470 nF 的耦合电容有更大的眼高。结合表3 和4 分析发现,100 nF、470 nF的耦合电容在不同速率下接收眼宽和TJ 抖动差别不大,在速率为6.25 Gbit/s 时100 nF 的耦合电容比起470 nF 的耦合电容眼宽和抖动几乎都有微小的改善,原因是远端PMA 测试时传输链路增加带来了更多的传输损耗且注入了抖动,耦合电容的影响被部分削弱,结果表现为100 nF 和470 nF 的耦合电容在眼宽和抖动上有最优的参数。

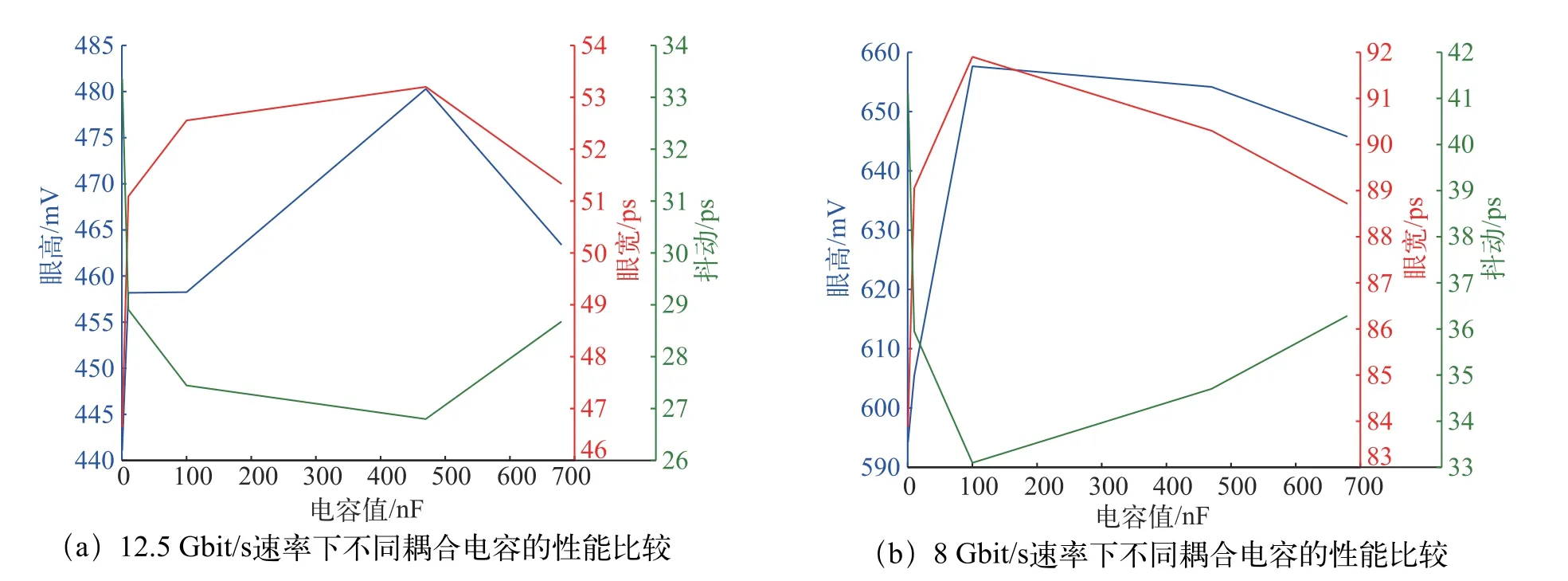

图4 12.5 Gbit/s 和8 Gbit/s 耦合电容性能仿真

综合本文的试验结果,表明在16 Gbit/s 以下的高速SerDes 传输中,使用100 nF 和470 nF 的AC 耦合电容满足理论分析的耦合电容选取标准,在不注入抖动时PDJ处于可接受范围,不会产生误码。以10.3125 Gbit/s 为界,100 nF 和470 nF 分别是最佳的选取方案。

以10.3125 Gbit/s 为界,分别对16 Gbit/s SerDes下经典的12.5 Gbit/s 和8 Gbit/s 速率的试验结果进行仿真,生成的仿真图如图4 所示。可以直观地看出,在12.5 Gbit/s 和8 Gbit/s 下,470 nF 和100 nF 的耦合电容均拥有最大的眼高、眼宽和最低的抖动,印证了之前的结论。

5 结论

本文基于公司自研的16 Gbit/s FPGA 芯片进行了研究,测试了16 Gbit/s 以下典型速率的SerDes 传输性能,并且考虑到SerDes 传输中AC 耦合电容的影响,通过理论分析和试验验证发现,在10.3125 Gbit/s 速率以下100 nF 的耦合电容具有更好的性能,而在10.3125 Gbit/s 速率以上时,选取470 nF 的耦合电容效果最好。相比于目前国外Xilinx 公司7 系列12.5 Gbit/s的SerDes 芯片,本文研究的16 Gbit/s FPGA 芯片在速率上有一定提升,且通过AC 耦合电容的选取保证了SerDes 信号的传输质量,为后续32 Gbit/s FPGA 芯片的SerDes 调试提供了参考。