SOI基光波导传输损耗的研究

李逸康,张有润,葛超洋,汪 煜,张 波

(1.电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054;2.中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

硅和二氧化硅的高折射率差可以实现硅基光电子器件的高密度集成[1-2],绝缘体上硅(SOI)材料在硅基光电子中大量应用。光波导是硅基光电子的基本结构之一,用于定向传输光,并起到连接光栅、多模耦合器等光电子器件,实现这些器件间光信号传输的作用。如何降低光在波导中的传输损耗,进而可以使用更低功率的光源是光波导研究中的一项重要课题,具有提高系统稳定性和可靠性的意义。为了降低传输损耗,首先要知道传输损耗的构成以及产生机理,从而为设计和生产更低损耗的光波导提供优化方法。

对于波长为1550 nm的光,硅材料波导的损耗理论上可以分为4部分:模式失配损耗、表面散射损耗、内部散射损耗和弯曲损耗[3]。弯曲损耗仅存在于弯曲波导中,光在波导中传输时,一部分光以倏逝波的形式存在于光波导的外部,这部分光在波导弯曲时受到波导的束缚小,导致光逸出波导,造成损耗,对于直波导,则不用考虑弯曲损耗[4]。模式失配损耗是光的模式和波导形状不匹配造成的。理论上,TE0模式在平板波导中传输不会产生任何模式失配损耗[5],但实际应用中波导截面是一个有限宽度的梯形,这意味着TE0模式在其中传播将产生模式失配损耗。表面散射损耗是由于波导表面不光滑导致的,波导传输光的本质是光的全反射,因此如果反射面不平整,就有可能不满足全反射条件,导致光在传播过程中发生散射。表面散射是不可避免的,但是通过特殊的工艺处理来获得更平滑的表面可以降低表面散射损耗[1]。内部散射损耗是由波导中的杂质和缺陷引起的,光遇到这些杂质或缺陷时发生散射。这些杂质或缺陷可能是在SOI衬底的生产过程中产生的,也可能是在后续硅基光电子器件的生产过程中引入的。

目前,对于低损耗波导的制作方法比较完善,波导的损耗机理也有较多研究,这些研究可以分为两类。第一类为在理论上提出波导传输损耗的机理,如AALTO等[5]研究了波导的模式理论、单模条件以及波导传输的损耗机理,从理论上把波导传输损耗和模式的关系进行了说明;LEE等[2]提出波导顶层硅面光滑程度一般较高,传输损耗中的表面散射损耗主要来自于侧壁,可以使用反应离子刻蚀的工艺方法来降低波导的传输损耗。第二类为从实际制作出发,设计并优化工艺来制作低损耗波导,如CASSAN等[6]设计了低损耗SOI基脊形波导,波导传输损耗达0.5 dB·cm-1;FORESI等[4]针对弯曲波导进行优化设计,在2 μm小曲率半径下,实现了90°转角的插入损耗低于1 dB。另外,对于非硅材料波导,DALDOSSO等[7]以氮化硅制作波导,得到针对730 nm和632.8 nm光的传输损耗接近0.1 dB·cm-1。

本文将目前文献中已经提出的波导传输损耗理论与实际制作的波导的仿真与测试分析相结合,提出了一种计算思路,计算出了实际波导传输损耗中3种损耗所占的比例。

2 实验测试

本文基于SOI衬底设计并制造了相同宽度的条形波导和脊形波导,通过有限差分本征模(FDE)仿真计算了波导的模式失配损耗,接着测试了条形波导和脊形波导的传输损耗,使用的方法为截断法[8]。本文提出的传输损耗测试结构如图1所示,该结构包含一组波导,在每个波导两侧制作光栅耦合器,除了波导长度之外,每个波导的其他参数均相同。对于每个波导,使用光纤和光栅耦合器进行光的输入输出,固定耦合输入光的强度,测试耦合输出光的强度,得到插入损耗。长波导插入损耗与短波导插入损耗的差值是波导长度差值导致的,因此插入损耗的差值除以波导长度的差值即为波导的传输损耗。

图1 硅波导传输损耗测试结构

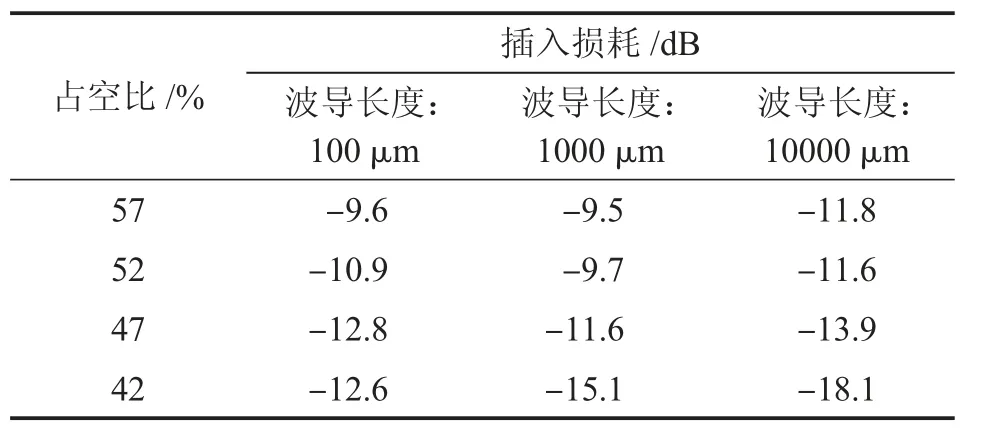

本文使用220 nm厚的顶层硅、5 μm厚埋氧层的SOI材料进行流片制作,SOI顶层硅使用的是电阻率为10 Ω·cm的硼掺杂p型硅材料,这是市面上常见的SOI材料规格,对应的掺杂浓度约为4.5×1014cm-3。条形波导和脊形波导的截面如图2所示。条形波导的宽度W1为500 nm,高度H为220 nm,脊形波导的宽度W2也为500 nm,刻蚀深度h为130 nm。制作的每组波导长度分别为100 μm、1000 μm和10000 μm。为了排除偶然误差,保证测试的准确性,根据光栅占空比的不同设计了4组实验,对每组实验测得的传输损耗取平均值,作为最后的结果。占空比指在一个光栅周期中未刻蚀的硅部分占总体的比值,不同占空比的光栅不影响传输损耗的测试结果。光栅耦合器的光栅周期为630 nm,刻蚀深度为70 nm,光栅的占空比分别设置为57%、52%、47%、42%。

图2 条形波导和脊形波导的截面

硅的刻蚀工艺是硅波导制作的核心工艺。针对硅波导和光栅的制作,三道硅刻蚀工艺为主流工艺,可以降低侧壁的粗糙程度和增加陡直度,从而降低波导的传输损耗[9]。三道硅刻蚀工艺指SOI顶层硅全刻蚀、刻蚀深度为130 nm的脊形波导刻蚀和刻蚀深度为70 nm的光栅刻蚀,两道非穿透性刻蚀是对顶层硅全刻蚀进行高精度套刻。硅光工艺对刻蚀精度要求较高,2 nm的波导侧壁粗糙度会引入2 dB·cm-1的波导传输损耗[10]。

在一个调节架上水平放置制作的波导样品,将输入光纤和输出光纤通过六维调节架基本固定在芯片两侧,并调整至光栅耦合器需要的耦合角度。使用1550 nm的激光器作为光源,连接一个偏振控制器。波导样品的输入光纤连接偏振控制器输出端,样品的输出光纤接光功率计。调节偏振控制器,确定输入光为TE模式。通过光功率计确定从偏振控制器输出的光强为0 dBm。之后进行细对准,通过六维调节架的调节旋钮将输出光纤中的光功率调整到最大值,此时光纤的对准位置达到最佳点,即此时光功率计的测量值为输出光功率,减去输入的0 dBm可以得到插入损耗。

测得的插入损耗如表1所示。对表1中的数据进行拟合,以占空比为57%的数据为例,100~1000 μm波导的插入损耗从-9.6 dB变化到了-9.5 dB,那么计算出900 μm的传输损耗为1.11 dB·cm-1,同理通过1000 μm和10000 μm的数据计算出9000 μm波导的传输损耗为-2.56 dB·cm-1,通过长度的加权平均,利用光栅占空比为57%的这一组数据计算出的传输损耗为-2.2 dB·cm-1。对其他几组数据做同样的处理,条形波导的传输损耗平均值为-2.4 dB·cm-1。对脊形波导使用同样的方法,得出传输损耗的平均值为-2.0 dB·cm-1。

表1 不同波导长度和光栅占空比下的插入损耗

3 仿真与结果分析

在FDE仿真软件中对制造的波导截面形状一致的条形波导和脊形波导进行仿真测试,仿真软件使用的是完全忽略内部杂质和缺陷的理想硅材料,即没有内部散射损耗,并且波导的表面是完全光滑的,即没有表面散射损耗,因此仿真得到的损耗为模式失配损耗。

通过显微镜得到刻蚀工艺制作结构的剖面图,得知实际工艺中刻蚀产生的侧壁角度约为81°。将一个截面底角为81°、高为220 nm、顶宽为500 nm的条形波导和相同宽度的脊形波导导入FDE仿真软件中,波导的光模式仿真结果如图3所示。可以看到,部分电场分布于侧壁表面,造成模式和光源的TE0模式不匹配,从而产生损耗。仿真得到的理想条形波导传输损耗为-3.0×10-11dB·cm-1,理想脊形波导传输损耗为-1.1×10-10dB·cm-1。考虑到仿真软件的精度有限,在仿真时网格的划分等因素会对仿真结果产生一定影响,因此仿真结果仅能说明模式失配损耗所占总体损耗的比例可以忽略不记。

有效折射率是评判光波导传输损耗的另一个重要参数,低损耗波导的制作也需要考虑波导宽度对有效折射率的影响。由于仿真难以模拟真实的波导粗糙表面,通常按照光滑波导进行仿真,因此通过对有效折射率的仿真,可以间接反映相同程度的表面粗糙度对表面散射损耗的影响。有效折射率是一个定量描述波导中单位长度相位延迟的量。有效折射率越高,说明波导对光的束缚能力越强,光以倏逝波的形式沿波导表面传输的部分越少,相同表面粗糙程度下,表面散射也相对越小。对于220 nm高的理想条形波导,TE0模式光的有效折射率和波导宽度的关系如图4所示,波导宽度在0.4 μm以内时,波导对光的束缚能力随波导宽度的减小而急剧下降,波导中在表面传输的倏逝波的比例上升,此时表面粗糙程度将加剧光的表面散射,不利于制作低损耗波导。

图3 条形波导和脊形波导的光模式仿真结果

图4 220 nm高的条形硅波导的有效折射率和波导宽度的关系

条形波导和脊形波导实验测试所得的传输损耗减去模式失配损耗之后,剩下的损耗还有内部散射损耗和表面散射损耗。由图3可知,光在波导中能量分布区域基本一致,并且条形波导和脊形波导是在相同衬底上以相同的工艺制作的,内部的杂质和缺陷理论上没有差别,因此认为条形波导和脊形波导的内部散射损耗相等。脊形波导的侧壁面积比条形波导小,因此脊形波导的表面散射损耗低于条形波导[5],且由于采用同样的工艺制作,相同侧面积下的散射损耗相等,条形波导与脊形波导的表面散射损耗之比等于刻蚀深度之比。

设测得的条形波导传输损耗为Ltl,脊形波导传输损耗为L'tl,条形波导的模式损耗、内部散射损耗和表面散射损耗分别为Lmo、Lis和Lss,各种损耗之间的关系应满足:

因此在Lmo、Lt1、L'tl和H、h已知的前提下,可以通过式(1)计算得出Lis和Lss。

对于条形波导,表面散射损耗为-1.42 dB·cm-1,占传输损耗的59.2%,这表示主要的光波损耗来自于表面的散射。内部散射损耗为-0.98 dB·cm-1,约占传输损耗的40.8%,表明材料中杂质或缺陷较多,这些杂质可能是在SOI衬底的生产过程中引入的,也可能是在光栅生产过程甚至是在测试过程中引入的。脊形波导侧壁面积较小,所以表面散射损耗也相对减小,仅为-0.58 dB·cm-1,占脊形波导传输损耗的29%,而内部散射损耗占传输损耗的71%。本次制作的条形波导的传输损耗和脊形波导的传输损耗高于目前论文中讨论的值,表明制作工艺有待进一步优化。占传输损耗较大比例的是内部散射损耗,尤其对于表面散射更低的脊形波导,其占了波导总损耗的71%,这说明本次工艺SOI的顶层硅掺杂浓度过高,或者后续刻蚀工艺对SOI表面硅晶体引入了缺陷。条形波导的表面散射损耗为-1.42 dB·cm-1,这比目前文献中低损耗波导的总传输损耗0.3 dB·cm-1还高[5],说明刻蚀工艺还有进一步优化的空间。

4 结论

本文通过条形波导和脊形波导的对比测试,以及条形波导测试损耗和FDE仿真损耗的对比,从理论上分析了几种不同原因的损耗所占总体损耗的具体比例,得知本次直波导的传输损耗主要是由波导表面散射和内部散射引起的,为以后如何制造出损耗更低的波导指明了改进方向,如使用更高电阻率的SOI材料来降低SOI中的杂质,在工艺过程中降低温度变化幅度来降低波导加工过程中引入的缺陷。