基于ATE 的千兆以太网收发器芯片测试方法

谢凌峰,武新郑,王建超

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

以太网技术在计算机网络发展的过程中起着十分重要的作用,由于其节点数目和传输范围不受限制且传输介质选择性多,现已成为网络技术中的重要部分。目前以太网技术按照传输速率可分为标准以太网(只支持10 Mbit/s 速率的数据传输)、快速以太网(最大传输速率为100 Mbit/s)、千兆以太网(最大传输速率可达1 000 Mbit/s)和万兆以太网(最大传输速率可达10 000 Mbit/s)[1-2]。

芯片测试是半导体产业不可缺少的环节之一,许多公司采用系统板对芯片进行测试,通过FPGA 输入激励信号,将输出信号与预期信号进行对比,判断芯片功能是否正确。但该测试方案无法进行芯片成品量产化测试,测试精度依赖外围设备,无法精确测试[1]。自动测试设备(ATE)能够解决上述问题[3],ATE 结合了计算机技术、自动化技术、通信技术、微电子技术和精密仪器测量技术[4-5],能够提供精确且可满足量产要求的测试方案。

针对千兆以太网测试技术的研究,既能为千兆以太网芯片提供设计验证测试,也能有效推动集成电路自动化测试的发展,为同种类型甚至功能更完善的以太网芯片提供测试思路。本文选择了一款千兆以太网芯片进行研究,设计了相应的外围电路,通过ATE 机台实现了千兆以太网芯片功能的测试。

2 千兆以太网芯片介绍

2.1 千兆以太网芯片功能

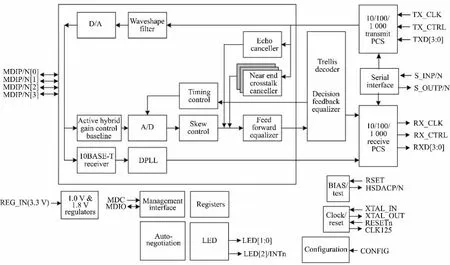

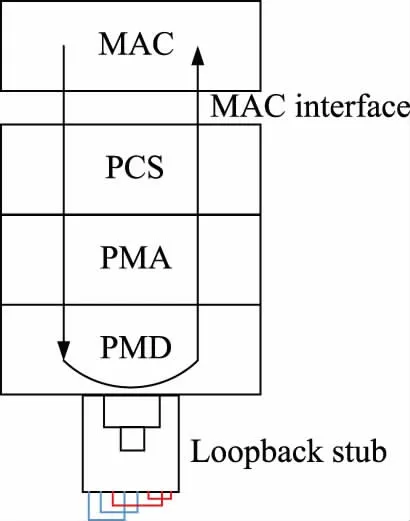

图1 千兆以太网芯片功能框图

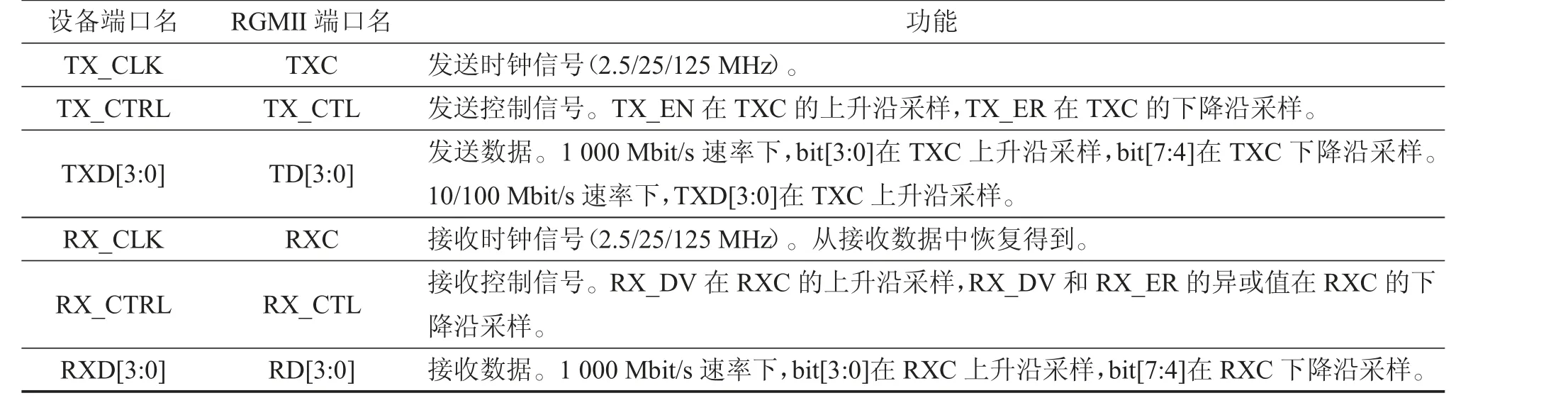

介质相关接口(MDI)包括MDIP/N[3:0] 4 对接口,在100BASE-T 和10BASE-T 模式中,只用到MDIP/N[1:0]作为接收/传输端,并未使用MDIP/N[3:2];而在1 000BASE-T 模式中则使用了MDIP/N[3:0]4对端口。串行吉比特媒体独立接口(SGMII)包含S_INP/N 和S_OUTP/N,简化吉比特媒体独立接口(RGMII)包含TX_CLK、TX_CTRL、TXD [3:0] 以及RX_CLK、RX_CTRL、RXD[3:0]。RGMII 接口功能见表1。

表1 RGMII 接口功能

本文选取的千兆以太网芯片支持铜介质接口和光纤介质接口。铜介质接口包括MDIP/N[3:0]4 对差分 信 号 线, 支 持 1 000BASE-T、100BASE-T 和10BASE-T 3 种协议模式;光纤介质接口则包括S_INP/N、S_OUTP/N 2 对差分信号线。

2.2 千兆以太网芯片配置

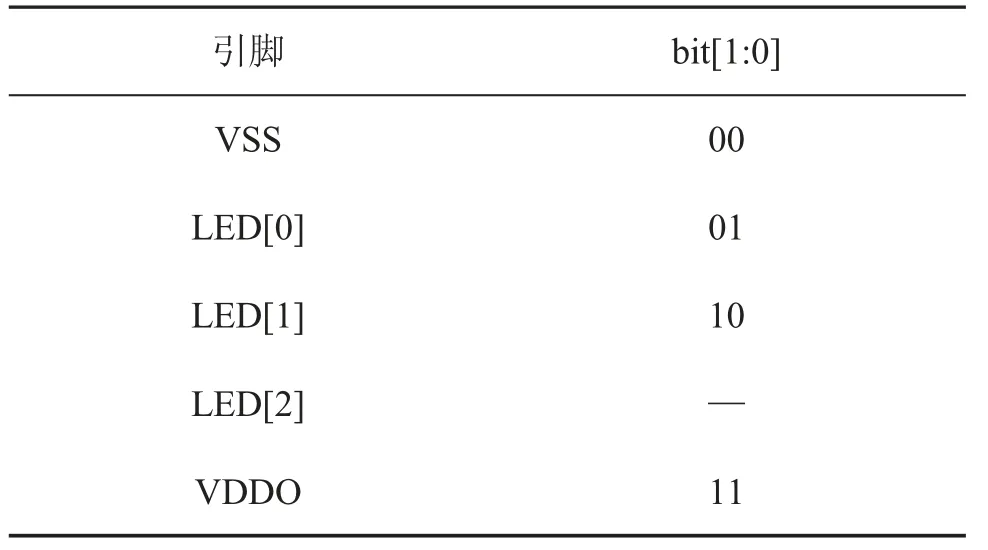

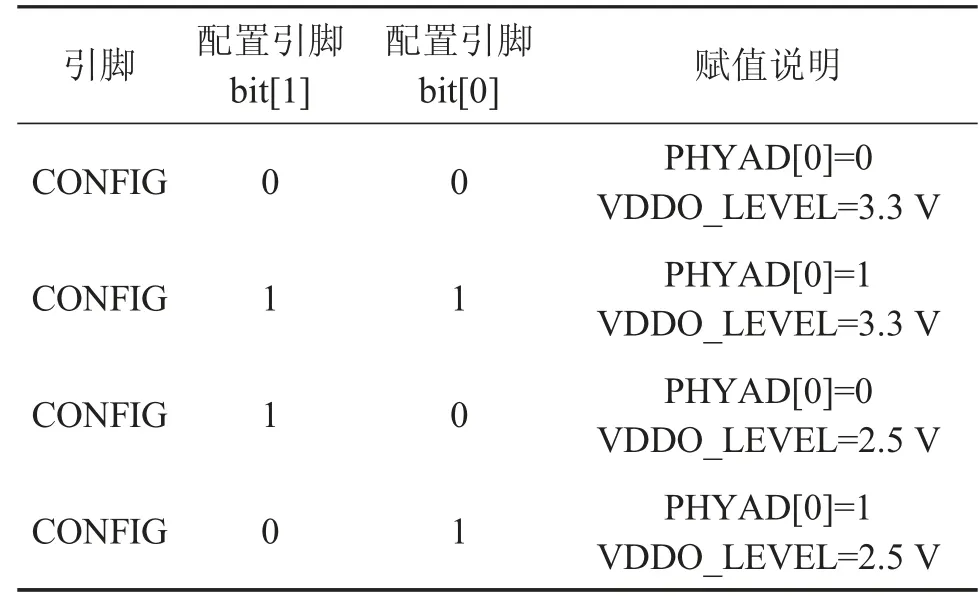

千兆以太网芯片有2 种配置方式:硬件配置和寄存器写操作配置。硬件配置主要通过CONFIG 引脚实现,根据CONFIG 连接的不同引脚来决定其所代表的2 位映射bit[1:0]。CONFIG 配置如表2 所示。

表2 CONFIG 配置

CONFIG 引脚的映射关系如表3 所示,其中PHYAD [0] 表示PHY 地址的最后一位(bit[0]),VDDO_LEVEL 则对应Page 2 Reg 24 寄存器的第13位:如果VDDO_LEVEL 为3.3 V,则Page 2 Reg 24 寄存器的第13 位为0;如果VDDO_LEVEL 为2.5 V,则Page 2 Reg 24 寄存器的第13 位为1。

表3 CONFIG 引脚映射关系

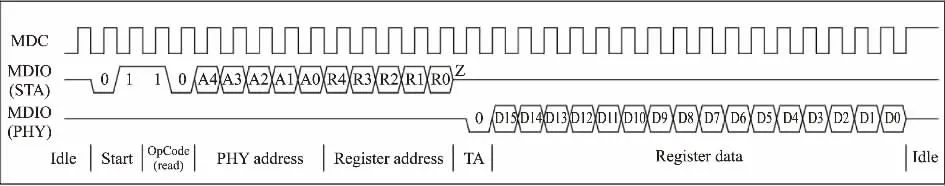

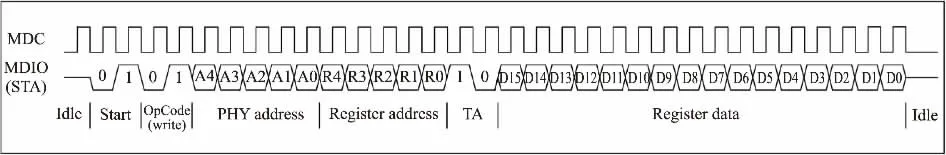

软件配置则主要依靠MDC/MDIO 接口实现。MDC 是管理数据时钟接口,最大时钟频率为12 MHz;MDIO 是管理数据输入/输出接口,是一个与MDC 同步的双向读写I/O 接口。MDIO 管脚需要接一个1.5~10 kΩ 的上拉电阻,在读写操作空闲时将MDIO拉高。典型的管理接口的读操作和写操作如图2、3 所示,MDIO 输入0110 时芯片判断为寄存器读操作,A4~A0 数据代表PHY 地址(默认为00000),R4~R0 数据为读出寄存器地址位;MDIO 输入0101 时芯片判断为寄存器写操作,通过R4~R0 数据得到写入寄存器的地址。

图2 MDC/MDIO 读操作

图3 MDC/MDIO 写操作

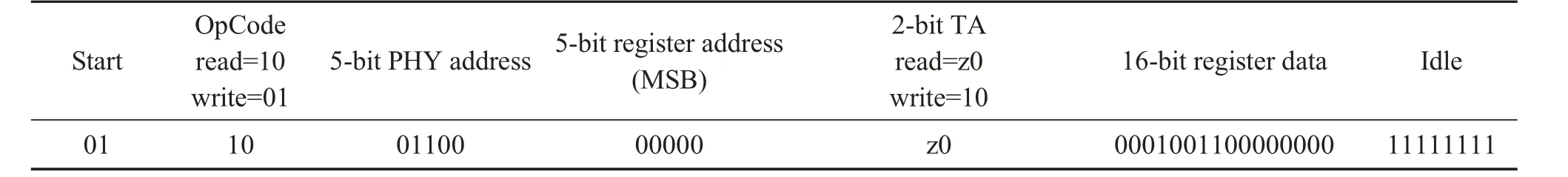

MDIO 读操作示例如表4 所示,PHY 设备地址为01100,访问寄存器地址为00000,16 位数据为0001001100000000。

表4 MDIO 读操作示例

3 外围测试电路设计

3.1 MDIO 读写测试电路设计

在本文所设计的千兆以太网芯片测试板上,CONFIG 引脚通过4 个继电器分别连接至VSS、LED[0]、LED[1]和VDDO。通过切换继电器可以方便地将CONFIG 引脚连至合适的管脚来选择VDDO 的电压。输入参考时钟信号XTAL_IN 管脚直连至测试机的数字通道上,查看手册得知此时钟频率为25 MHz,在实际测试码中,测试机的频率设置为250 MHz,10 行XTAL_IN 测试码为一个周期,频率为25 MHz。

3.2 回环测试电路设计

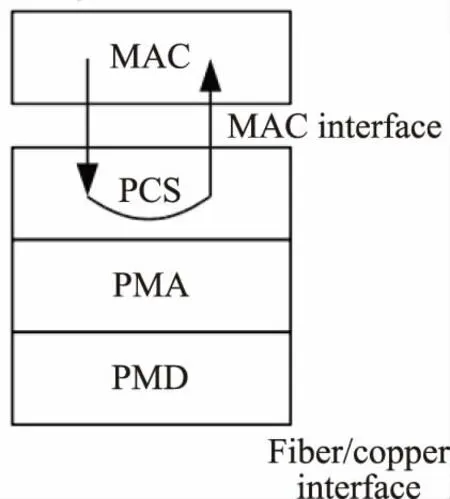

回环测试是以太网收发器芯片一种比较便捷且有效的测试方案,在以太网芯片回环模式下,芯片从MAC 层接收到的数据不会通过MII 接口发送出去,而是通过回环又被送回MAC 层[6],传输速率由寄存器Page 2 Reg 21 的bit[6]和bit[13]决定,00 对应10 Mbit/s,01 对应100 Mbit/s,10 对应1 000 Mbit/s。本文所进行的回环测试主要分为PCS 回环测试和stub回环测试,原理如图4、5 所示。PCS 回环用于验证MAC 接口及PCS 层的逻辑功能;stub 回环则用于验证整体数字电路的逻辑功能。

图4 PCS 回环测试原理

图5 stub 回环测试原理

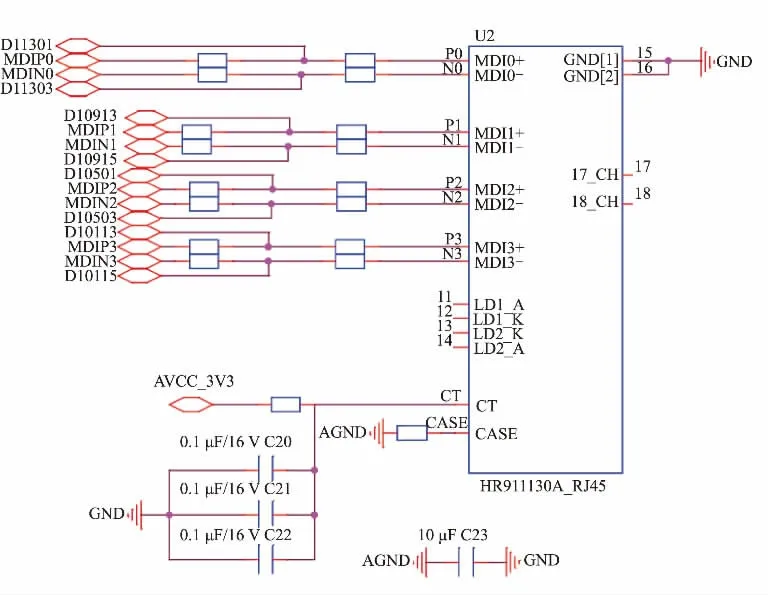

对于10BASE-T 和100BASE-T,回环测试不需要配置寄存器,而对于1 000BASE-T 模式的回环测试,需要配置寄存器Page 6 Reg 18 的bit[3]为1 来激活外部回环模式,回环测试中千兆以太网芯片的MDIP/N[3:0]直接连接至内部集成变压器的RJ45 网口HR911130A上,其网口的接法和外围电路设计如图6、7 所示。

图6 回环测试网口接法

图7 RJ45 网口外围电路设计

4 ATE 测试机台实现

4.1 寄存器读写测试

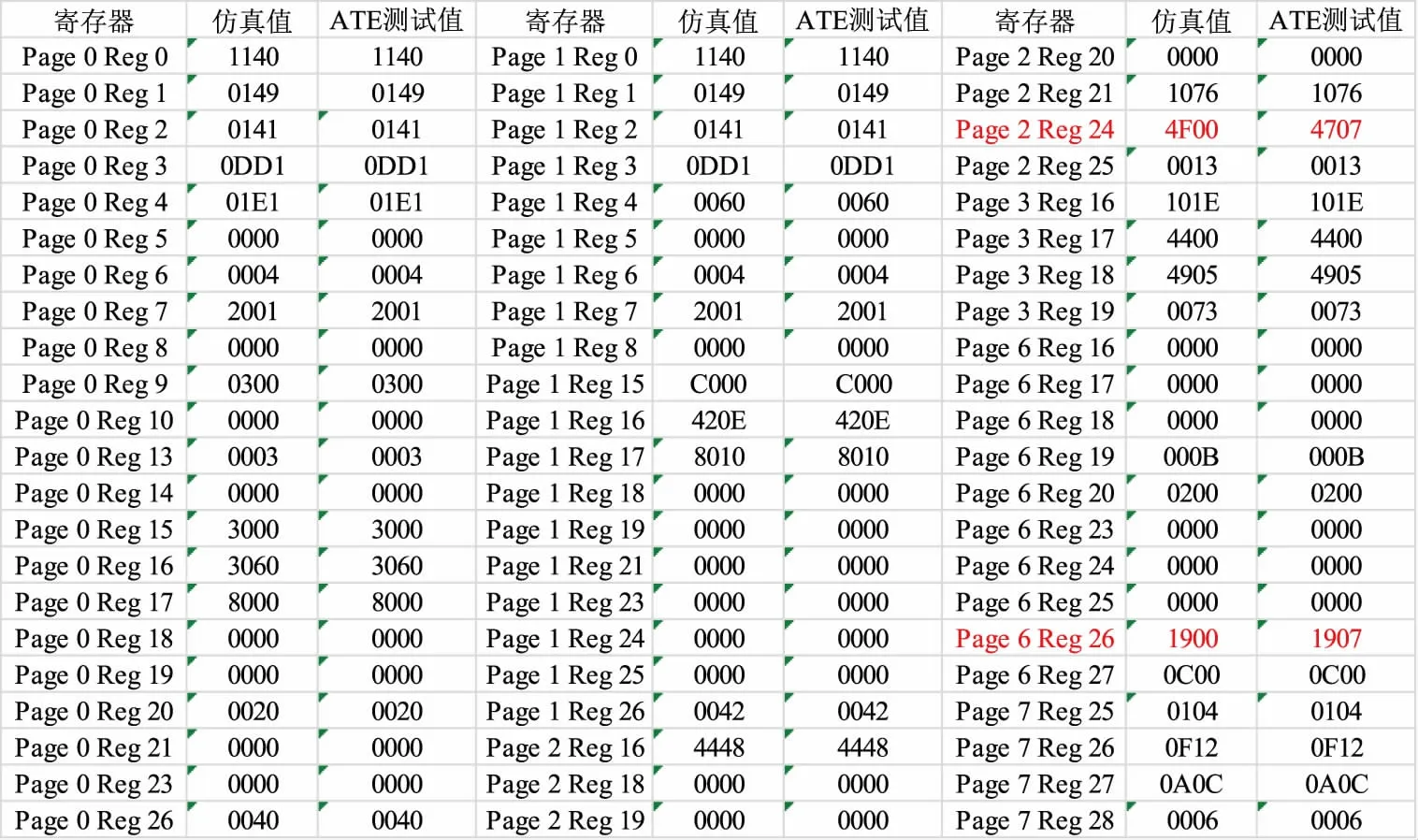

本文所研究的以太网收发器芯片的寄存器组共计有0~9、12、14、17、18 这14 页,通过MDIO 接口读默认值、再写入并读出值[7],部分仿真和测试结果如图8 所示。在ATE 测试中有2 个寄存器读出来的数值与仿真结果不同,其中Page 2 Reg 24 寄存器的ATE 测试数据为4707(0100011100000111),仿真结果为4F00(0100111100000000),经查手册,该寄存器低12 位为预留位,并无实际意义,可以忽略;Page 6 Reg 26 寄存器的ATE 测试数据为1907(0001100100000111),仿真结果为1900(0001100100000000),经查手册,该寄存器的低4 位为温度显示,由于测试实际环境并不能保证与仿真温度一致,该4 位寄存器值也可忽略。将上述2 个寄存器值修正后,功能测试项通过,即千兆以太网芯片通过MDIO 读写测试。

图8 寄存器读写仿真及测试结果

4.2 回环测试

本文进行的回环测试主要分为10 Mbit/s、100 Mbit/s、1 000 Mbit/s PCS 回 环 测 试 和10 Mbit/s、100 Mbit/s、1 000 Mbit/s stub 回环测试。测试机通过验证相应标志寄存器、RX_CTRL 跳高和RXD[3:0]数据以判断回环测试的正确性。由于千兆以太网芯片属于异步芯片,每次在RXD[3:0]采集到的数据都会出现前后位移的现象,本文使用Digital Capture 工具抓取RX_CTRL 信号变高后的RXD[3:0]数据,将此4 位数据与输入端TX_CTRL 变高后的TXD[3:0]数据进行比较,RXD[3:0]数据对应的十进制数与TXD[3:0]数据对应的十进制数一致,则表明接收数据正确,继续比较下4 位数据。在实际测试过程中,输入端口TXD[3:0]共有148 个数据用于测试,每个输出端口RXD[3:0]的每位数据均与TXD[3:0]的对应位数据进行比较,回环测试结果为通过,即表明输出端口的每一位数据均与输入端口的对应位数据一致,即以太网收发器芯片能够将输入端的数据正确输送至输出端输出。按照上述方法测试了6 种不同模式的回环,输出端的数据均正确。

回环测试标志寄存器的读出值如表5 所示,在6种回环测试中,对应的标志寄存器值均正确,表明芯片处于正确的工作模式中,RXD[3:0]接收到的数据经比较也和TXD[3:0]发送的数据一致,千兆以太网芯片在十兆、百兆、千兆速率下能够正确发送数据,并通过回环接收到相应的数据,验证了该芯片功能的正确性。

5 结论

本文介绍了千兆以太网芯片的功能描述和配置方法,基于ATE 测试机台给出了寄存器读写测试和回环测试的外围测试电路,基于ATE 抓取输出端数据,并与输入端送入的数据进行比较,验证了千兆以太网芯片的功能正确性,为千兆以太网芯片测试提供了一定的参考。