基于16 nm FinFET 工艺FPGA 的低功耗PCIe Gen3 性能研究

季振凯,杨茂林,于治

(无锡中微亿芯有限公司,江苏无锡214072)

1 引言

高速总线是高性能通信的关键,其广泛应用在雷达探测、图形加速及网络适配等领域[1-3]。与众多数据传输接口相比,高速串行总线(PCIe)具有点对点差分传输、强抗电磁干扰及高数据传输带宽等优点。随着大数据时代的到来,新兴的应用场景更注重高速总线的高带宽、低延时及高灵活性,PCIe 与FPGA 的集成技术能够显著提升总线的灵活性,可满足新兴领域的需求。

高性能与低功耗是FPGA 电路与PCIe 模块集成技术的核心竞争力。2002 年,Intel 公司联合业界20 余家企业共同起草第三代I/O 总线PCI Express 协议[4]。在新一代系统通信中,PCIe 已经成为和上位机高速通信的主流协议。2017 年,蒲恺等使用28 nm 制程FPGA内部集成的PCIe 与上位CPU 进行通信,其实际带宽可达180 MB/s,占总线带宽的50%以上[5]。2022 年,沈洋等在28 nm 制程的FPGA 与雷达系统的通信中提出了一种由FPGA 发起的组数据传输(Block DMA)的传输流程,以降低数据传输过程中CPU 的参与度,进而解放CPU 的算力[6]。然而,在FPGA 与上位机进行高带宽通信时,会出现电路表面温升过高进而影响通信质量并增大系统功耗的现象,需要在系统设计时额外增加冗余散热装置并提升散热等级,因此市场需要一种低功耗且高可靠的FPGA 电路[7-8]。为提高FPGA 电路中PCIe 运行的稳定性,降低运行电路的温升、功耗以及系统的冷却成本,本文针对16 nm FinFET 工艺的FPGA 的PCIe Gen3 建立充分完备的性能评估方案,以探究先进工艺制程下超大规模集成电路中PCIe Gen3 的性能稳定性及低功耗性。

本文以16 nm FinFET 工艺SRAM 型FPGA 为研究对象,搭建针对低功耗PCIe Gen3 的高速通信的性能测试、温升测试以及三温(-55~125 ℃)功耗测试方案,以检测其在PCIe 通信时的低功耗特性及性能稳定性。采用不同数据长度的数据包来对PCIe 与CPU 通信架构进行测试,并针对PCIe 底层高速串行收发器(SERDES)进行高速口眼图参数测定,为全面评估新工艺技术下的产品可靠性提供支持。

2 FinFET 工艺低功耗FPGA 的PCIe 电路架构

2.1 FinFET 晶体的电子调控特性

自1965 年4 月摩尔定律被提出以来,半导体技术始终按照其预测的方向发展,直至集成电路的规模从早期的50 只晶体管发展到亿门级规模。受限于物理尺寸,在将制程推进到纳米级别时,制造技术壁垒及良品率导致的成本呈指数上升。除成本因素外,传统的平面晶体管在制程接近20 nm 时,在高温环境下,电路内部漏电及电子失控等现象会显著增强。为进一步提升芯片稳定性,在降低晶体管特征尺寸的同时半导体产业界也通过提升制造工艺的方式来推进产业升级。

与传统平面晶体管相比,FinFET 晶体管工艺大大降低了晶体管的启动电压,在改善电路电性能的同时也降低了电路的整体功耗[9]。图1 为平面晶体管与FinFET 晶体管的示意图,传统的平面晶体管与源/漏极的接触面是单独的平面矩形,而FinFET 晶体管的栅极对沟道的键合面变成了门式接触面。在三个接触面中,突起鳍式的两侧面是栅极的主要调控面,立体的接触结构不仅增大了栅极对载流子的控制能力,也提升了晶体管的电参数稳定性及抗辐射性能[10-11]。

图1 平面晶体管与FinFET 晶体管示意图

2.2 PCIe 协议及有效带宽

PCIe 协议需要设备核心以及PCIe Core 两个组件,其中设备核心负责与Core 进行交互并实现事务的发起及接收。PCIe 按照实现功能的不同,可划分为事务层(TLP)、数据链路层(DLLP)及物理层(PLP)。图2为PCIe Core 结构分层示意图,TLP 负责接收设备核心发来的指令并将信息按照范式转换成TLP 数据包,或者将接收的TLP 数据包进行校验、翻译并将信息传递给设备核心。DLLP 在逻辑上链接TLP 与PLP,DLLP 主要负责DLLP 数据包的打包/解包、冗余数据备份、错误包识别及传输数据流控制等。PLP 是PCIe的数据口,负责转换或拆解PLP 数据包。

图2 PCIe Core 结构分层示意图

PCIe 协议的理论传输带宽与协议的Gen 值有关,Gen1 下的PCIe 的速度带宽为2.5 Gbit/s,Gen3 将其提升到8 Gbit/s。由于PCIe Gen3 采用128 bit/130 bit 编码,且TLP、DLLP 及PLP 在进行转换时会在数据包的包头及包尾加上起始数、DLL 协议包、点对点循环冗余校验(ECRC)以及链路循环冗余校验(LCRC),导致PCIe 的实际传输带宽相比理论值有额外的开销。PCIe Gen3 的理论最大带宽(Tmax,单位为MB/s)为[12]

其中,PL为传输数据(Payload),N 为传输通道,OV包括起始数、DLL、包头码、ECRC 以及LCRC 校验值。

PCIe 数据包组成示例如表1 所示,在PCIe 协议中,除Payload 区间为0~4 096 B 及Header 为12/16 B外,其余数据包大小固定。在Gen3 中,当PCIe 传输数据格式为256 B、Header 为16 B、通道为8 时,其理论最大带宽Tmax为7 219.9 MB/s。

表1 PCIe 数据包组成示例

3 低功耗FPGA PCIe Gen3 性能测试方案

3.1 PCIe 测试设备

本实验所用的低功耗FPGA 器件(简称DUT)采用16 nm FinFET 工艺,其封装形式为倒装,内部集成PCIe Gen3 硬核,对照电路(简称CD)为国外同类型FPGA 电路,其工艺制程为28 nm,支持PCIe Gen3。实验所用的设备包括高速示波器、高速误码仪、多路温度测试仪及直流电源,硬件为SERDES 测试板和PCIe转接板,测试连接的上位机为带有16 通道PCIe 插槽的PC。测试设备简介如表2 所示。

表2 测试设备简介

高速示波器用来检测DUT 的高速口收发眼图,评估PCIe 的底层高速口的传输质量;误码仪用来提供高频收发信号,评估DUT 在高速收发时的抗干扰能力;四路直流电源用来为电路的内核、端口、辅助以及高速口部分提供电源,其余模块电源供给由适配器提供;多路温度测试仪用来记录电路在动态运行时的温度变化趋势。

3.2 PCIe 与CPU 通信架构

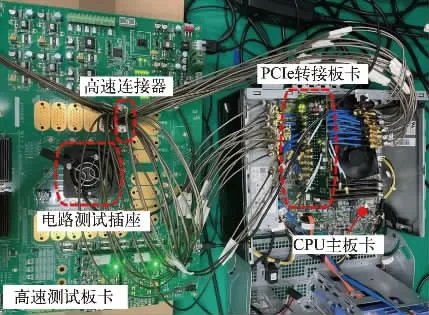

被测电路内嵌三组PCIe Gen3 集成器IP,各组之间能够独立进行×8 的通信传输,即最大可调用24 路差分串行高速收发器进行通信。图3 为PCIe 通信连接图,在PCIe 与CPU 通信时,需将DUT 置于SERDES测试板内,通过一组高速光纤与PCIe 转接板进行连接。PCIe 转接板最大支持PCIe×16 金手指通信及热插拔。

图3 PCIe 通信连接图

PCIe 测试由高速测试板卡、高速连接器、PCIe 转接板卡以及CPU 主板卡共同完成。该硬件方案并未将FPGA 的SERDES 管脚与PCIe 物理约束固定,因此可实现电路片上任意高速口区域与上位机的PCIe 通信。更换三温测试插座后还可对电路进行三温测试。将待测电路放入电路测试插座中,选择要测试的SERDES区域作为PCIe 的接入高速口区域。PCIe Gen3×8 测试使用任意两个相邻区域,将对应区域的TX、RX 和参考时钟信号全部引出,与自研的PCIe 转接板进行逆序连接。TX 端采用直连方式连接,RX 端添加一个100 μF 的隔直器进行滤波。高速连接器接口形式为BullsEye 接口,使用专用的20 Gbit/s 高速线缆进行连接。

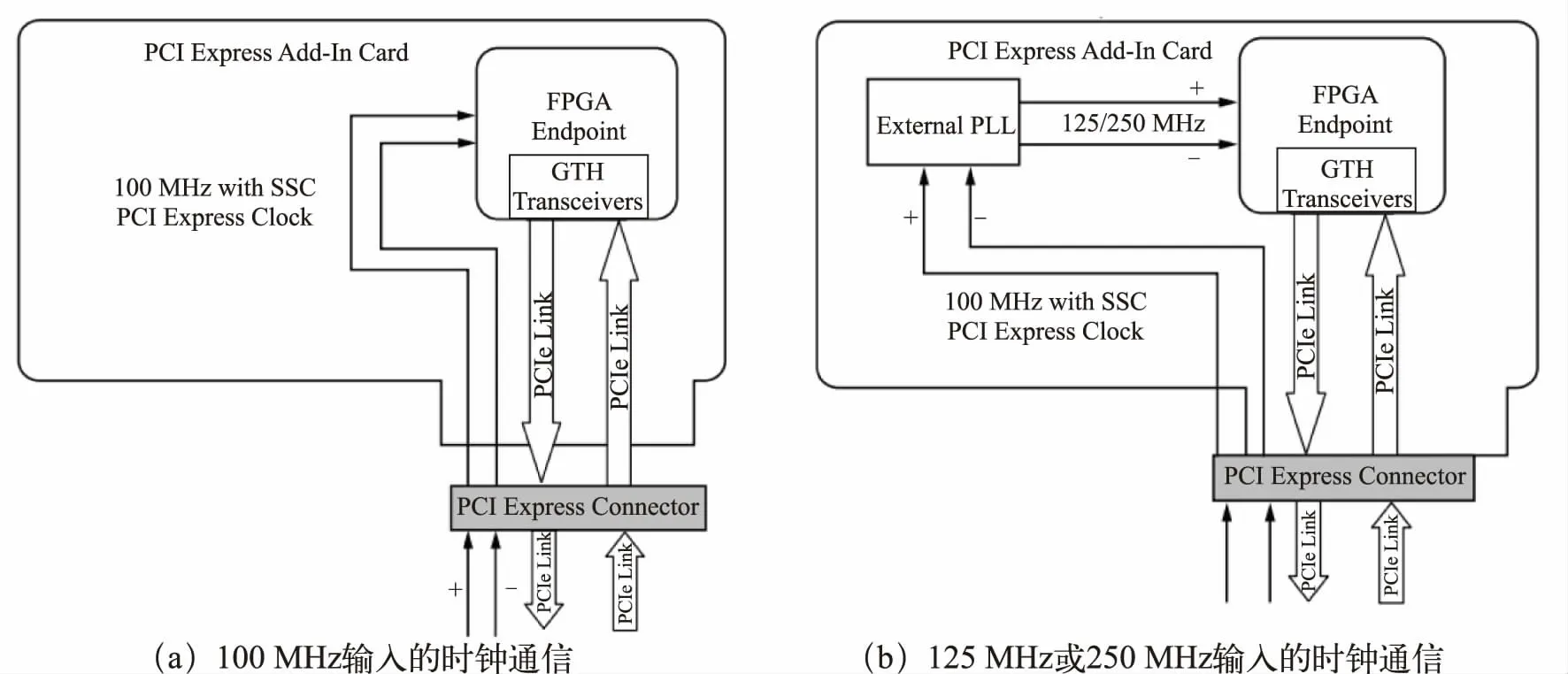

在完成物理连接后,接收功能块与发送功能块在电路与CPU 通信时需要建立同源时钟通道。在初始的差分信号传输中,PCIe 总线会进行比特交互,即在链路上交替传输一段0 和1 序列,用来给接收端提取数据时钟。除数据时钟外,PCIe 参考时钟是以100 MHz为源头产生的扩频时钟。扩频时钟可用于所有子设备,即每个链路设备共享相同的时钟源。PCIe 时钟通信示意图如图4 所示,本方案的参考时钟频率为100 MHz,由上位机CPU 提供,此时的PCIe 总线可直接将参考时钟引入,当使用125 MHz 或250 MHz 参考时钟选项时,须使用FPGA 内部的锁相环(PLL)进行5/4 和5/2 的乘法,实现100 MHz 时钟到125 MHz和250 MHz 时钟的转换。

图4 PCIe 时钟通信示意图

4 FinFET 工艺FPGA 器件的PCIeGen3 性能

4.1 PCIe 与CPU 实际通信带宽

建立电路与CPU 的通信,采用PCIe Gen3 并调用8 路串行收发器来完成与上位机的数据交互。在编译工具中调用MARK_DEBUG 命令对PCIe 的各组件状态进行监控,监控的对象包括cplllock、qplllock、cfg_ltssm_state 等状态。cplllock 以及qplllock 用来标识驱动时钟是否满足高速收发时所需的精度与质量,cfg_ltssm_state 用来表示链路训练的状态。链路训练是一个动态的过程,上位机CPU 与电路在上电后按照PCIe 协议的LTSSM 进行链路协商以达到最优的速率以及宽度。图5 为LTSSM 状态机实测图,被测电路在实测过程中cfg_ltssm_state 的状态为10,对应链路训练的L0,即已经实现通信。

图5 LTSSM 状态机实测图

建立与CPU 的通信链路后,FPGA 与CPU 开始数据交互,为降低与上位机命令交互的时间以提升传输效率,本次读写压力测试采用上位机一次指令包含n 组DMA 数据包信息的方式进行。典型的PCIe 传输过程中,CPU 每次在发起DMA 传输时都需要设置每一帧DMA 数据的相关信息并进行编解码操作,严重干扰PCIe 传输效率。FPGA 与CPU 交互流程如图6所示,本次软件测试方案中CPU 在完成链路建立后向FPGA 一次发送n 组DMA 的起始地址以及上报地址等信息,以降低CPU 解析数据的压力,提升与FPGA的交互效率。

图6 FPGA 与CPU 交互流程

本次PCIe 压力测试为非连续读写测试,为精准计算读写带宽,循环测试时数据包的字节长度选择512~4 096 B。上位机速率检测软件为内部开发的PCIe测试软件,可实时显示速率。PCIe 带宽压力测试结果如图7 所示,经过读写压力测试,测得传输4 MB 的数据包时,其读速率可以达到3 907 MB/s、写速率可以达到4 430 MB/s,分别为理论最大有效带宽的54.1%和61.4%,可以满足实际传输的带宽吞吐需求。

图7 PCIe 带宽压力测试结果

4.2 PCIe 物理层高速眼图

通过高速示波器监测被测电路中SERDES 的高速收发质量,通信频率为8 Gbit/s、通信数据格式为PRBS7。通过对比CD 与DUT 中高速通信的差异来分析DUT 的传输稳定性及信号质量。监测的主要指标包括眼宽、眼高及信号抖动,信号抖动主要体现在总抖动(TJ)上,按照抖动来源可分为确定性抖动(DJ)和随机性抖动(RJ)。DJ 向下可分为占空比失真、码间干扰和周期性抖动。8 Gbit/s 眼图实测结果如图8 所示。

图8 8 Gbit/s 眼图实测结果

在通信频率为8 Gbit/s、码型为PRBS7 的设置下,DUT 的眼图脉络与CD 基本一致,两者的整体信号质量较为稳定。眼图参数的均值及标准方差如表3 所示,DUT 以及CD 的眼高均值分别为324.69 mV 和334.88 mV,说明DUT 在高速通信时眼图的张开度与CD 基本一致。在信号抖动方面,DUT 的TJ、DJ、RJ 分别为18.766 ps、10.661 ps、578.95 fs,略低于对照电路的20.151 ps、11.366 ps、627.46 fs,说明DUT 在高速通信时眼图的抖动略优于CD。在信号定时误差TIE 参数上,DUT 的均值为2.1982 fs,比CD 的均值低40.0%,说明DUT 的时钟峰-峰值偏移更小。

表3 眼图参数的均值及标准方差

4.3 PCIe Gen3 温升测试

对电路进行PCIe Gen3×8 运行温度测试,首先将电路放置进PCIe 测试板插座中实现与上位机之间的通信,然后将多路温度仪的电耦合引线贴合在电路的上表面进行表温测量。常温下将PCIe Gen3 程序烧录进电路中后,在观测到PCIe 正常运行后进行高速功率及温度测定。高速功率等于电源内核以及高速口电源的功率之和。由于PCIe×8 需要用到8 路高速收发器,因此在高速运行的过程中物理层有着较大的开支来完成数据收发。温度测定主要用来表征电路的内部漏电及电子失控程度,CD 采用传统的平面CMOS 晶体管工艺,制程为28 nm,DUT 采用16 nm FinFET 工艺,其内部采用的门式接触结构能有效增强对电子的控制进而降低电路升温[10]。

DUT 的温升相比于CD 更低,其常温功耗相比于CD 也有显著的降低。电路表温及高速功耗对比如图9所示,当电路运行到30 min 时,DUT 的表温为30.6 ℃,低于CD 的37.5 ℃。从表温上升趋势来看,DUT 温升不显著,电路的温度在上升到30.3 ℃之后变化趋势较平稳,最后稳定在30.6 ℃左右,比CD 低18.4%;CD 的表温一直在升高,在10~15 min 时依然保持一定的上升趋势。在高速功耗方面,DUT 在室温运行时其功耗开支维持在1.54 W 左右。在PCIe 程序运行中,FPGA内部的SERDES 收发器、DCM、CLB、BRAM 等资源均会被调用,设计工艺的区别导致DUT 在高速运行时整体功耗更小。

图9 电路表温及高速功耗对比

4.4 PCIe Gen3 三温功耗

对电路进行PCIe Gen3 三温动态功耗测试,将电路放置进三温插座后,启动三温设备,待设备达到设定温度后,保持5 min,待FPGA 温度达到设定温度后,启动与CPU 的通信并开始记录功率。测试选用三颗DUT 和一颗CD,温度测试节点选择-55 ℃、25 ℃、125 ℃。选用数据包的字节长度为4 MB 的读写程序,所 测 定 的 功 率 等 于 VCCINT、MGTAVCC 及MGTAVTT 电路的功率之和。电路三温功耗对比如表4 所示。

表4 电路三温功耗对比

DUT 三温功耗比CD 低,尤其是在高温125 ℃条件下,电路的整体功率增加明显,DUT 平均功耗比CD低41.9%。在-55 ℃下运行时,DUT 整体功耗相比常温时有一定程度的降低,整体功耗比CD 低10.8%。

5 结论

本文以16 nm FinFET 工艺SRAM FPGA 为对象,探究FinFET 晶体管的电子调控特性、PCIe 协议及有效带宽,搭建针对低功耗PCIe Gen3 的高速通信的性能测试、温升测试以及三温功耗测试方案,实现对先进工艺制程下超大规模集成电路中PCIe 的性能稳定性及低功耗性的探究,其结论如下:

(1)在被测电路与CPU 通信过程中,电路与CPU通信稳定,PCIe 读写速率分别可以达到3 907 MB/s、4 430 MB/s,达到理论最大有效带宽的54.1%、61.4%;

(2)通过高速眼图测定,在通信频率为8 Gbit/s、通信格式为PRBS7 时,被测电路以及对照电路的眼高均值分别为324.69 mV、334.88 mV,两者眼图张开度以及抖动基本一致;

(3)在电路温升以及三温PCIe 功耗测试中,被测电路在常温下的表面温度比对照电路低18.4%,被测电路在125 ℃下的功耗比对照电路低41.9%。

该工艺下的电路能够稳定运行PCIe Gen3 总线,并在低功耗、低发热状态下实现高质量的PCIe 信号传输。