高密度陶瓷封装电设计中噪声控制研究

杨轶博,丁荣峥,高娜燕,李欣燕

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 概述

随着集成电路封装体朝小型化、薄型化和轻量化方向发展,电路集成功能不断增多,芯片频率和速度的提高使电路封装内部走线、过孔和内外引脚尺寸减小,封装密度增大。对于介电常数较高的陶瓷封装,由多种因素引起的信号噪声将对电路的信号和电源完整性产生无法忽视的影响[1,5]。

从本质上看,信号噪声源于传输线电气特性参数与数字信号电压电流波的相互作用。陶瓷封装互连中的信号噪声包括反射(会引起上冲、下冲和振铃效应)、串扰和同步开关噪声(包括电源弹跳和地弹跳,即SSN)。反射产生于电互连阻抗不匹配处,串扰产生于信号互连线间电磁场的相互干扰,同步开关噪声是由于电源和地网络阻抗以及覆电源/地层布局不合理[1,5]。

传输线设计是基于噪声控制的封装电设计的核心内容。广义上讲,传输线是引导电磁波沿一定方向传输的导体、介质或由它们组成的导行系统[1,2]。具体来说,在封装外壳/基板内部,传输线包括了走线、过孔、电源/地层和介质四部分。封装电设计主要通过选择传输线的材料(包括导体材料和介质材料)、控制传输线的尺寸和布局,来控制信号在通道中的反射、信号通道之间的串扰以及同步开关噪声等问题。

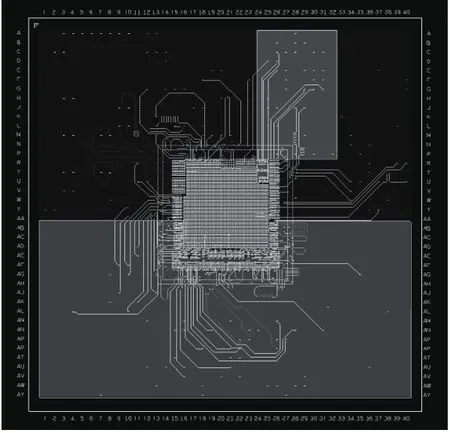

本文通过对封装互连噪声问题中反射、串扰和同步开关噪声的分析,利用Cadence16.3 Sip软件,设计了一款高频高密度陶瓷基板FC-CLGA1572。

2 信号反射

2.1 反射现象与原理

反射是传输线的基本效应,在信号沿传输线传播过程中,遇到阻抗不连续点就会产生反射现象。在时域图中,反射表现为实际电平围绕逻辑高/低电平上下波动,根据信号波形分为过冲、下冲和振铃[1]。在封装基板内部,存在走线转角、走线与过孔连接处以及细线与粗线连接处颈部(neck);封装基板与具有固定特征阻抗的芯片和PCB板连接。若以上连接处两侧的导体特征阻抗不同,信号就会产生反射,并在导体中传播。反射使导体中产生噪声,严重的噪声与信号叠加,可能导致正常工作的电路出现逻辑错误。

2.2 信号反射分析

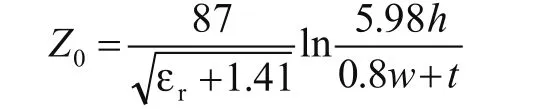

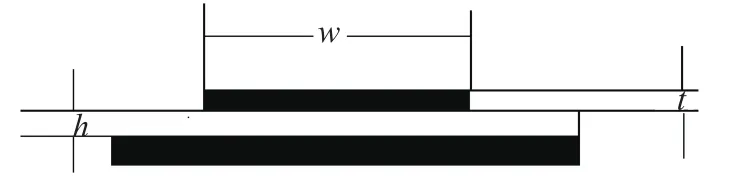

影响反射的根本原因在于特征阻抗是否匹配。对于传输线,特征阻抗由走线宽度、厚度、介质层厚和介电常数εr决定。其中,微带线的特征阻抗[1]为:

带状线的特征阻抗为[1]:

h、w、t如图1和图2所示[1]。

图1 带状线模型

图2 微带线模型

在控制反射噪声的设计中,需重点考虑“走线临界长度”。假设只发生一次反射,当源段与反射点间走线长度较短时,在源端信号还未上升至高电平时,反射信号就已经回到源端,被“淹没”在上升沿中。上升沿的波形失真对信号波形的影响不大。若源段与反射点间走线长度超过一定长度,发射端信号已升至高电平,反射信号才回到源端,此时的反射信号叠加在高电平位置,从而造成干扰。

因此,源端与反射点间的距离对反射噪声有重要影响,这一距离称为临界长度。临界长度不是固定值,它与电磁波在介质中的传播速度以及信号的上升沿相关。对于介电系数较大的介质,信号传播速度较慢,要求临界长度相应减小,对于上升沿短的信号(高频高速信号),也需减小走线的临界长度。

图3 Cadence Sip16.3中参数化计算特征阻抗(部分)

2.3 FC-CLGA1572基板防反射设计

FC-CLGA1572是一款针对高频高速芯片设计的陶瓷基板,芯片信号最高工作频率5 GHz,上升沿为215 ps。封装布线设计主要从匹配芯片与封装特征阻抗、控制布线长度和布线连接三个方面控制反射。

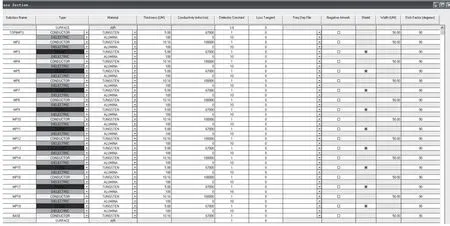

(1)匹配芯片与封装特征阻抗

Cadence Sip 16.3根据介质材料介电常数εr、介质单层厚度h、导体厚度t和走线宽度w,可自动计算出封装走线的特征阻抗。参数设置的目标是使封装特征阻抗与芯片特征阻抗相匹配,同时在此封装特征阻抗值确定的基础上,再根据陶瓷外壳导体印刷工艺调整h、w、t这三个参数,既满足阻抗匹配保证传输线中信号低反射率,亦兼顾陶瓷外壳制造工艺。

(2)控制布线长度

布线长度对反射的影响主要体现在“走线临界长度”上,在FC-CCGA1572封装设计中,控制布线长度即是保证走线尽量沿着芯片引出端(芯片凸点)到外壳/基板外引出端(焊球/焊柱焊盘)之间的最短距离,既减小该布线的长度,也为其他临近走线提供了走最短距离的空间。

(3)布线连接控制

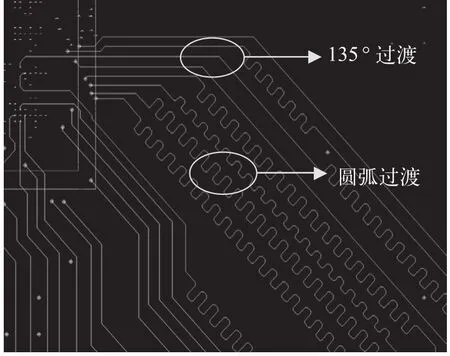

走线通常由几条线段衔接而成。电流在衔接段密度增大,增大程度由衔接两线段的角度决定:越接近180°,阻抗和电流密度越小,越接近90°,阻抗和电流密度越大。通常采用135°或圆弧过渡连接,在实测中,两种连接方式对反射影响不大。如图4所示,两线段采用135°衔接,蛇形走线(等延时时序设计)采用圆弧过渡。

图4 典型走线过渡设计

3 信号串扰

3.1 串扰现象和原理

串扰是指信号在传输线上传播时,因电磁耦合对相邻传输线产生不期望的电压噪声[1]。串扰至少由一对信号线组成:由于自身逻辑电平发生变化,对其他信号产生影响的称为干扰线;受到干扰,逻辑电平发生异常的信号线称为被干扰线。串扰只发生在干扰信号电平跳变的阶段。

串扰来源于信号路径与返回路径间存在的电磁场,它不仅限于信号和返回路径之间,一部分在周围空间延伸,称为边缘场。当一条传输线处于另一条传输线边缘场的范围时,这条线上就会出现串扰噪声,这正是串扰现象产生的根本原因。

3.2 封装串扰分析

在封装布线设计中,影响串扰的因素主要有三点:两线间距与两线平行长度、干扰源信号频率及上升时间、信号线与临近地平面间电介质厚度。

3.2.1 线间距和平行长度

线间距P和平行长度L与串扰噪声分别成反比和正比。P增大,串扰噪声减弱;L增大,串扰噪声增强。

3.2.2 干扰信号频率和上升时间

干扰信号频率f和信号上升时间与串扰噪声分别成正比和反比关系。随着f增大,串扰噪声增强;上升时间增加,串扰噪声减弱。

信号的上升时间也是影响串扰的重要因素。有仿真试验表明[1],对于同一布线结构,通过相同频率信号的相邻传输线,采用早期工艺上升时间为6 ns的驱动源在相邻信号线上产生的远端串扰峰值不足0.5 V,采用上升时间为0.5 ns的驱动源则在相邻信号线上产生了近3 V的远端串扰峰值。

3.2.3 传输线种类及信号/地间电介质厚度

在相邻导体平行长度、间距、信号频率、上升时间均相同的条件下,传输线的种类(微带线或带状线)及介质厚度均对远端峰值串扰值产生影响。在相同情况下,微带线比带状线在临近走线将产生更大的串扰噪声电压。

干扰源的信号线与地平面间介质层厚度对被干扰信号也有明显影响。相同种类的传输线,介质层厚度增大,在临近传输线上产生的串扰电压噪声越大。

基于以上分析,在封装电设计中可采用以下方法抑制串扰噪声[4~6]:

(1)增加导体线间距,减小高频信号线与相邻信号线的平行长度;

(2)对于微带传输线和带状传输线,将走线与地平面距离保持在0.25 mm内,可以显著减小串扰;

(3)如布线空间允许,在串扰严重的两线间插入接地走线,可以有效隔离干扰源的电磁波,从而减小串扰噪声;

(4)重要的高速信号可设计成差分对,利用信号差分特性有效降低串扰影响;

(5)相邻层的信号走线尽量按照正交布线,以减小耦合面积,降低串扰噪声。

3.3 FC-CLGA1572基板防串扰设计

FC-CLGA1572用于封装的芯片,其包含40个5 GHz和数百个1.6 GHz的信号通道,这些信号均相邻排列,节距仅为200 μm左右。频率高、节距窄且集中分布,使得封装设计过程需对这些信号进行严格的防串扰控制。

根据高频信号封装设计中的“3W”[2,3,7]准则,对5 GHz信号线间及与其他信号线加严设计要求,将线间距控制在4 W,即4倍线宽。对1.6 GHz频率的信号,按照“3 W”准则控制线间距。对于相邻层两条高速信号走线,为减小电磁耦合面积,降低串扰噪声,以正交方式走线。并选用氧化铝介质材料,单层瓷厚100 μm,介质厚度降低有利于控制远端峰值串扰电压的影响。

图5 针对5 GHz和1.6 GHz信号走线的间距设置

4 同步开关噪声[8]

4.1 同步开关噪声现象和原理

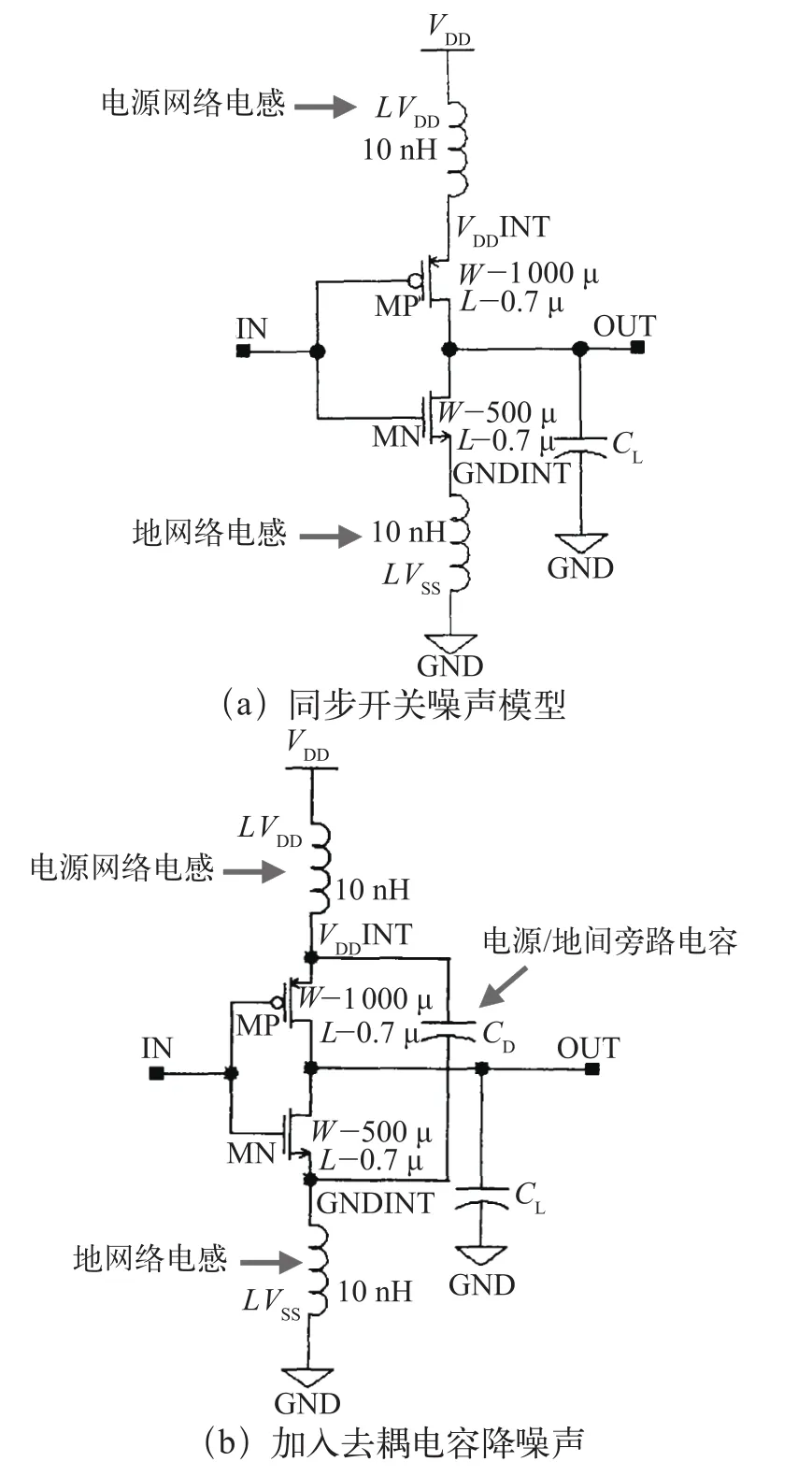

多个器件或多个门电路同时处于开关状态时,会产生瞬间变化的大电流,即较大的di/dt。电流经过回流路径时,由于电感的存在,形成交流压降,从而引起电压噪声。这种噪声称为同步开关噪声(SSN)。在传统理论中,SSN研究的对象是整个电路系统,包括芯片、封装和PCB板,同步开关噪声描述的现象在封装层面被称为电源弹跳和地弹跳。随着封装复杂程度的提高,在有机材料介质的HDI基板和陶瓷材料介质的高密度多层基板中,集成了原有PCB的功能,包括引入了电源层和地层(代替了传统的电源/地线和引脚)。因此,高密度封装陶瓷基板可利用SSN理论中系统的观点来进行分析。

4.2 同步开关噪声分析

影响封装同步开关噪声的因素包括两个:多个门电路瞬间同时产生的电流总量和封装中回流路径的电感。门电路开关电流是芯片本身的功能,且随着芯片向高频高速方向的不断发展,门电路翻转速度不断提高(di/dt不断增大),SSN对信号/电源完整性的影响程度不断增大。因此,在封装电设计中只有不断降低回流路径的电感才能保证电路功能满足使用要求。

降低同步开关噪声的关键就是降低封装回流路径即电源网络和地网络的总电感值。

通常,降低封装回流电感常用的设计包括以下两种:

(1)增加封装中电源和地路径的互感,电源和地引脚应成对分布并尽可能靠近布置,以增大电源和地平面的互感;

(2)对电源供电电感进行旁路,如加入旁路电容可为高频交流信号提供低阻通路。

图6展示了典型SSN噪声的电路模型和加入旁路电容进行去耦降噪的电路模型。

4.3 FC-CLGA1572基板降低同步开关噪声设计

FC-CLGA1572采用倒装芯片形式,具有低寄生电感的优势(相比于引线键合方式)。但为保证封装电设计最优,采用了两种方法降低封装基板中电源/地网络寄生电感:

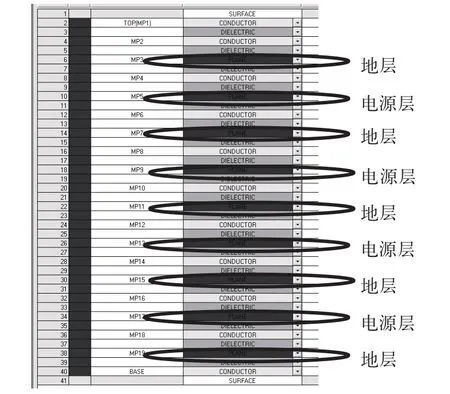

(1)增大电源/地层互感,形成“天然”旁路电容

封装整体布局采用电源层-地层-电源层-地层间隔分布的方式,拉近了地层和电源层的距离。如图7所示。

(2)降低地平面电感

降低地平面电感的方法主要是保证相邻信号线走线在地平面有完整投影。对于高频信号,其阻抗的主要部分是感抗。横跨同层中多个地金属区会显著增加地平面回流感抗。这将加剧SSN噪声对信号完整性的影响。

为降低FC-CLGA1572封装地平面电感,设计采用图8所示布局。地层MP3由三个独立的金属区域VSS、USBPHY_VSSA和VSS_DDR组成,信号层为MP2层。MP2层所有走线在MP3层的投影绝大部分都位于三个金属区域中单独的某一个,而不是横跨两个或三个金属区。

图7 FC-CLGA1572电源层与地层间隔排布图

5 总结

本文主要介绍了陶瓷封装电设计中常见的反射、串扰和同步开关噪声三种信号/电源完整性问题。通过原理和影响因素分析,结合FC-CLGA1572陶瓷封装基板设计,提出了解决方法,保证了信号反射、串扰和同步开关噪声符合电路要求,可供大家进行高密度陶瓷封装设计参考。今后工作还需通过电性能仿真,对暴露的信号/电源完整性问题进行针对性设计改进,进一步提高电路电性能。

图8 FC-CLGA1572降低地平面阻抗设计

[1] 陈伟. 高速电路信号完整性分析与设计[M]. 2009.

[2] 解析特征阻抗[Z].奥肯斯培训资料.

[3] 陈思思,等. 信号完整性中的串扰分析[J]. 2005, 10.

[4] 李文斌,等. 高速电路中过孔的仿真分析[J]. 2010, 2.

[5] Richard K Ulrich, et al. 高级电子封装[M].

[6] Roger Dame. Vias, Structural Details and their Effect on System Performance [Z]. Design Con, 2012.

[7] Huabo Chen. Effects of 20-H Rule and Shielding Vias on Electromagnetic Radiation From Printed Circuit Boards [Z].

[8] Asanee Suntives. Using Via Fences for Crosstalk Reduction in PCB Circuits[J].

[9] HaoHsiang Chuang. Signal/Power Integrity Modeling of High-Speed Memory Modules Using Chip-Package-Board Co-analysis[J].

[10] 陈建华. 基于IBIS模型的CMOS电路同步开关噪声的计算和优化[J]. 2001.