SOI抗辐射先进技术研究

藏 鑫,纪旭明,谢儒彬

(中国电子科技集团公司第五十八研究所,江苏无锡214035)

1 引言

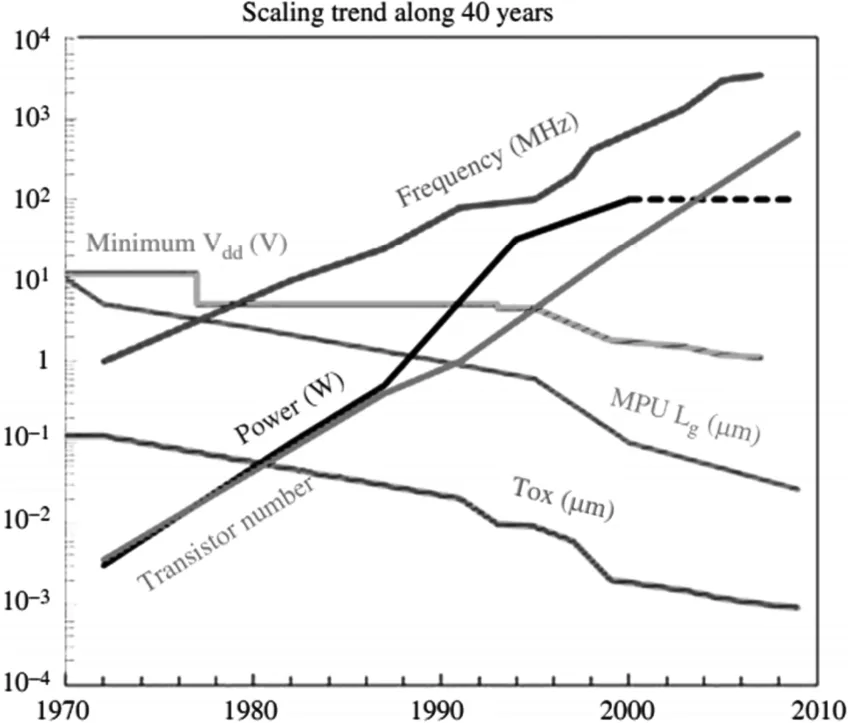

在近四十年的时间中,主要CMOS技术参数发展趋势是基于Dennard经典等比例缩小原则。这一原则是集成电路制造技术中最有效的提升器件性能和降低能耗的方法。但随着器件特征尺寸减小,短沟效应、量子隧穿以及寄生效应等问题的出现使得传统微电子器件技术逐渐难以满足集成电路技术持续发展的需求,限制了集成电路的集成度、可靠性以及电路性能。

SOI是一种三层结构的新型硅基半导体材料,通过绝缘层实现了器件和衬底的介质隔离,SOI具有以下的优点:

①由于采用绝缘介质隔离,器件与衬底之间不存在电流通道,消除了体硅器件中常见的闩锁效应,提高了电路的可靠性;②具有良好的抗辐射特性;③减小了寄生电容,运行速度提高了20%~35%,器件功耗减小了35%~70%[1];④抑制了衬底的脉冲电流干扰,减少了软错误的发生;⑤与现有的硅工艺兼容,可减少13%~20%的工序。

自1970年代以来CMOS技术参数整体发展趋势如图1所示。

2 SOI在抗辐射领域的应用

由于SOI CMOS电路实现了完全的介质隔离,PN结面积小,不存在体硅CMOS技术中寄生的场区MOS管和可控硅机构,因此辐射产生的光电流可以比体硅CMOS电路小近三个数量级,使SOI电路在抗单粒子事件、瞬时辐射等方面有着突出优势。

图1 最近四十年主要的CMOS技术参数趋势

2.1 单粒子事件(SEU)

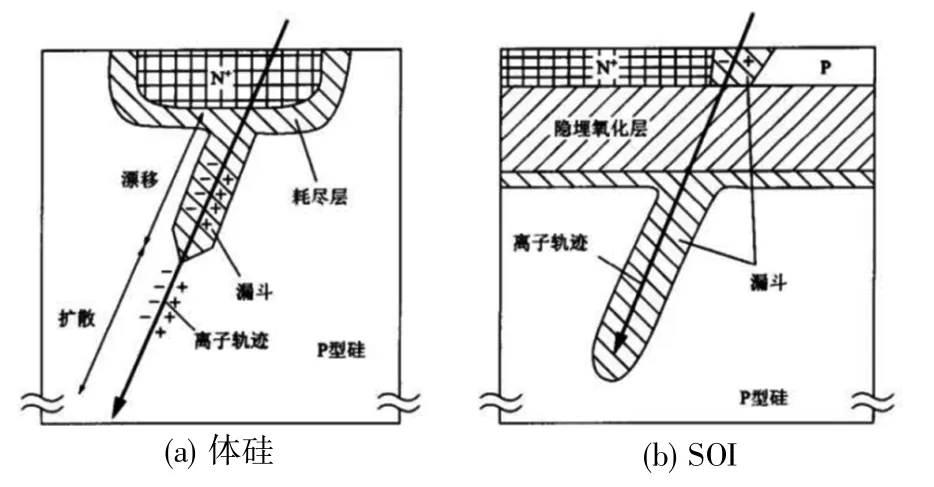

当一个高能粒子入射到器件中的反偏的PN结耗尽区及下面的体硅区时,沿着粒子运行的轨迹硅原子被电离,产生电子空穴对的等离子体。沿这个轨迹附近PN结耗尽层发生短时塌陷并且使耗尽层电场的等位面变形,耗尽层变形区又称为“漏斗”。

在SOI器件中,入射的粒子也将沿着它的轨迹使硅发生电离。然而,由于在有源区和衬底之间存在着隐埋绝缘层,只有那些在薄SOI顶部硅膜内产生的电子才能够被收集。一般情况下的抗辐射应用中,SOI硅膜厚度为150~300nm,因此,在硅中产生的电离化轨迹长度比值就是SOI在抗SEU的加固性能方面优于体硅器件的一级近似。能量粒子不同材料条件下的射入情况如图2所示。

图2 能量粒子的射入情况对比

SEU的幅度是以线性能量转换(LET)为单位表示。定义为:

其中,x为沿着粒子轨迹的直线距离,dW为粒子损失的并被硅吸收的能量,mv是硅的质量,LET常以MeV·cm2/mg为单位来表示。由SEU产生的电子-空穴对可以表示为:

其中,w是产生一个电子-空穴对所必须的能量。在电子收集过程中,有可能会产生约1~10mA的SEU电流尖峰。由于SOI中收集电子的有效轨迹长度的减少,使得SOI器件中SEU电流尖峰比体硅器件中的小50倍(对约200nm的SOI膜而言)。

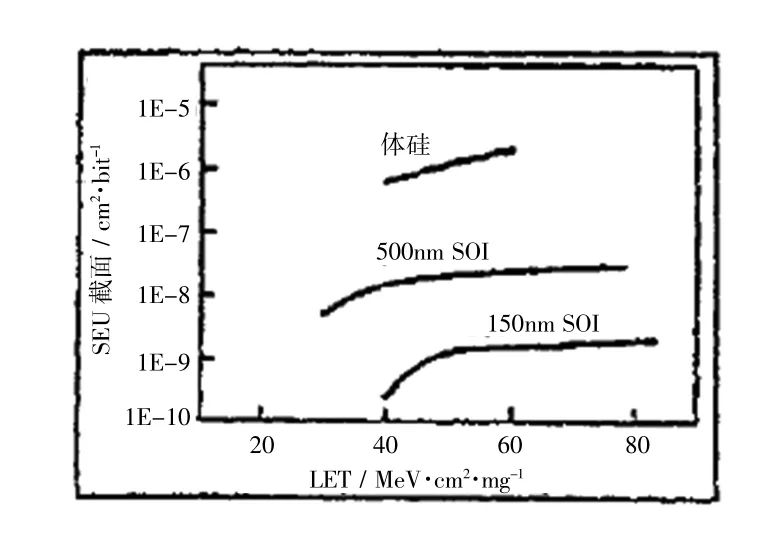

图3中给出了体硅和SOI电路的SEU截面。SEU截面以每逻辑位的等效面积(cm2/位)为量度单位。该截面越小,器件对辐射就越不敏感。可以看出,在抗辐射强度方面,150nm厚的SOI器件比500nm厚的SOI器件提高了10倍,比体硅CMOS器件提高更多。

图3 体硅和SOI电路的SEU截面

2.2 剂量率效应

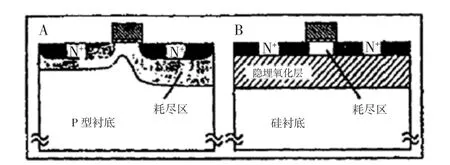

在日辉或核爆炸事件中,在很短的时间间隔内淀积大剂量的电磁能量,这就会产生剂量率效应。剂量率单位是rad(Si)s-1。1rad(Si)辐射在硅中产生约4×103/cm3电子-空穴对。能量在短时间内就被吸收,会在器件的耗尽区中产生明显的光电流,产生的光电流可以表示为:

式中,q为电子荷,Vdept是耗尽区的体积,g是载流子在硅中的产生常数,等于4.2×1013空穴-电子对/cm·rad(Si)s-1。

在传统CMOS器件中,这一光电流会引起闩锁,对于SOI器件,由于实现了完全的介质隔离,不存在体硅CMOS技术中寄生的场区MOS管和可控硅结构,而且具有较小的PN结耗尽区体积,如图4所示。因此辐射产生的光电流比体硅CMOS电路小近三个数量级,有很强的抗瞬时辐射能力[2]。

图4 体硅和SOI MOSFET中的耗尽区体积

2.3 总剂量辐射效应(TID)

总剂量辐射效应是累积剂量的电离辐射效应,通常以γ表示总剂量。电离辐射在SiO2中形成空间电荷机制如下:

电离辐射在SiO2中激发电子-空穴对,一部分会被SiO2中的深空穴陷阱俘获成为正的固定空间电荷。在正偏压下,这些固定空间电荷比较多地集中在Si/SiO2界面附近。空穴在SiO2中的迁移过程有两种模型,即激化子迁移模型和多极俘获模型。

电离辐射在Si/SiO2界面产生界面态。所谓界面态就是在Si/SiO2界面处存在于禁带中的能级和能带,他们可在很短的时间内和半导体硅交换电荷。界面态在器件工作或测试过程中会和硅体内交换载流子而使界面上带电状态发生变化[3]。产生和影响Si/SiO2界面的因素很多,电离辐射就是其中的一类。当未复合的空穴完全穿过SiO2时,空穴会在Si/SiO2界面或SiO2-栅极界面附近被俘获,即:

式中,fT为空穴俘获率;Nht为陷阱密度;σht为空穴俘获截面;ΔΧ为陷阱分布宽度。空穴俘获率可以从1%变到100%,取决于SiO2的质量和作用在其上的电场强度。在Si/SiO2界面辐射诱生的陷阱密度可以有几个数量级的增加。

界面态的建立比空穴在氧化层中输运更慢。如果在栅极上加负偏压,产生的陷阱量更低,在低温下几乎没有陷阱产生。

2.4 各类器件对比

由于SOI器件的有源区体积小,而且是全介质隔离,所以漏电流比体硅电流低。如前所述,在这些工作条件中,SOI器件优于体硅 CMOS器件,SOIMOSFET与体硅器件相比具有抗SEU和抗γ辐射性能。SOI电路也无闩锁效应,但是在体硅CMOS中,SEU或者γ射线的光电流却可以触发闩锁效应。对于SEU或γ辐射,SOI电路优于体硅CMOS电路,目前SIMOX存贮器电路(64KSRAM)具有SEU失效率为10-9/位·天(最坏情况下的地球同步轨道失效率)并且在1011 rad(Si)/s的剂量率辐射下仍能保持电路功能。这些数字表明,与体硅电路相比,SOI电路的抗辐射强度提高了100倍。

3 抗辐射特性研究现状

国内从80年代以来先后开展SOI技术研究的单位有:中国科学院上海微系统与信息技术研究所(原上海冶金研究所)、北京大学微电子所、清华大学微电子所、北京师范大学、东南大学、复旦大学、吉林大学、中国科学院半导体所、微电子中心等。国外研究SOI技术起步更早。以美国为例,美国圣的亚哥国家实验室提出了辐射加固计划,图5给出了该实验室在未来几年中所采用的加固技术和生产的加固产品。可见,0.25μm CMOS/SOI将在未来几年里在加固 256KSRAM、FPGA、Mixed-SignalASICS以及加固Pentium技术中占有越来越重要的地位[4]。圣的亚哥实验室的加固技术包括LDD工艺、RH浅结隔离、Si3N4侧墙、多晶硅和S/D区与硅化钛合金、50k/sq的SEU去耦电阻、平整的互联介质等加固工艺。

图5 圣的亚哥国家实验室辐射加固计划

Honeywell公司的RICMOS工艺已能在生产中实现厚度为15nm的氧化层、650 nm的有效沟道长度为和50 Mrad(Si)的抗辐射总剂量。该公司已商品化的HX6156系列256KX1STATICRAM-SOI产品被主要用于航空航天及军工电子领域,其抗总剂量水平达到1×106rad(SiO2),抗剂量效率水平达到1×1011rad(SiO2)。由该公司生产的SOIHX2000门阵列具有大于1×106rad(Si)的总剂量辐射、大于1×1012rad(Si)/s的辐射剂量率以及1×1012errors/bit/day的单粒子辐射效应的能力,且其抗中子注量可达1×1014/cm2。

在处理器方面,Harris公司为美国政府提供的RH3000系列32位抗辐射产品及标准的航空器用计算机(SSC)可以说是其中的典型代表。它应用SOI技术,其抗辐射水平达到1Mrad。它所有的功能都集成在两片芯片上,确保了性能稳定、可靠。在轨道上运行时,基本型SSC寿命为2a,第一代SSC寿命为5a,而第二代SSC可以达到10a以上。

法国的Thomson-CSF公司采用SOI技术,应用多层布线和1.2μm及0.8μm的设计规则,制备了抗总剂量和重粒子加固CMOS电路,包括16k/64k/256k的SRAM,8位/20MHz的A/D转换器,以及数字和逻辑ASIC电路。

4 SOI发展新趋势

4.1 应变沟道

在SOI的发展中遇到较大的问题就是硅器件电子迁移率和空穴迁移率偏低。因此,人们开始致力于研究提高顶层电子迁移率的结构。将应力引入SOI MOS沟道以提高载流子迁移率的技术目前倍受重视。相对于采用其他高迁移率半导体材料,采用这项技术对CMOS器件的制造工艺影响最小。

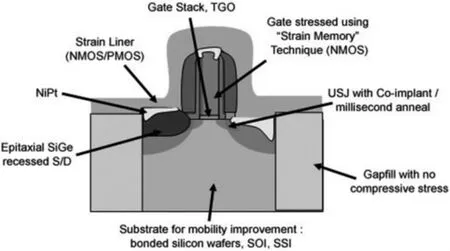

2006年6月Freescale宣布了应用应变SOI衬底的先进CMOS技术。利用该技术能够有效降低电路的功耗和改善电路的性能。用sSOI技术[5],一层Si放置在SiGe衬底上,Si原子将因SiGe晶格而得到拉伸,如图6所示。该技术可使电子移动速度增加70%;sSOI晶体管的性能可因此比常规器件的性能提高30%,功耗则降低40%。

图6 s-SOI MOS器件示意结构

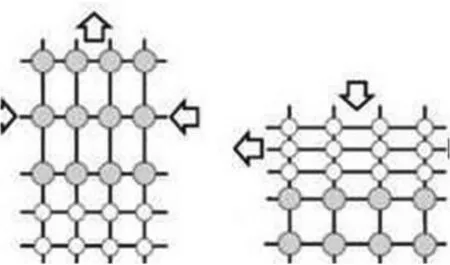

目前研究较多的一种方法是在沟道区采用Si/SiGe异质结构,由于Si材料和SiGe材料晶格间存在差异,被用作通道材料。在此种结构中,或者是在Si层中产生拉应力,或者是在SiGe层中产生压应力,如图7所示。例如有一种结构是沟道区采用应变Si/弛豫SiGe结构,在应变硅层中引入双轴拉应力,能在MOSFET通道中诱导高达1.6GPa的局部应变,这种情况可以使电子和空穴迁移率均增大,增加CMOS电晶体的导通电流。

图7 Si/SiGe异质结构应力方向示意图

4.2 薄埋层的SOI材料

一般使用的薄膜SOI材料埋层厚度均在100nm以上,埋层材料通常为SiO2。然而,在部分耗尽型SOI结构中,沟道下方的硅层中仅有部分被耗尽层占据,由此可导致电荷在耗尽层以下的电中性区域中累积,造成所谓的浮体效应;且SiO2由于埋层存在,热导率比较差。

为了解决这些问题,人们开始寻求薄埋层的SOI材料,同时也要保持良好的SiO2的绝缘性[6]。薄埋层SOI材料的埋层厚度一般在50nm左右,有的低至20nm甚至更薄。薄埋层SOI一般用于低压器件,一方面保持了绝缘体上硅的优良结构,另一方面埋层有优良的导热性能,是低压绝缘体上硅的一个发展方向[7]。

随着器件沟道长度的不断减小,短沟道效应越来越严重。降低沟道效应的一个有效方法就是减小源-漏结深。已知SOI器件硅膜层的厚度的降低类似于体硅器件中结深的减小,当器件尺寸进入纳米尺度,就要采用超薄硅膜SOI器件。其结构与SOI器件相同,只是硅膜层厚度很薄[8]。基于此特点,该器件具有以下优点:可有效切断漏电途径,大幅度降低关态漏电流,降低功耗;可有效抑制短沟道效应、DIBL效应;结电容减小,提高开关速度,同时降低寄生电容的影响;无浮体效应。

然而,超薄硅膜器件也存在一些问题:很薄的硅膜层会引入很大的源-漏寄生电阻;会引起载流子迁移率降低、阈值电压增大,导致开态电流降低;在超薄硅膜的情况下,掺杂浓度对阈值电压的调整作用不是很明显,需要通过金属栅来调整功函数,进而改变阈值电压。

5 结束语

SOI技术有着体硅技术不可比拟的各种优势,尽管目前仍存在很多没有解决的问题,例如如何生产低成本高质量的SOI材料等问题,但是与体硅CMOS器件相比,SOI器件具有较小的寄生电容、抗辐射、耐高温等特性,使其必将逐步取代体硅材料,在民用、军事等方面获得更广泛的应用。随着研究的深入和技术水平的不断进步,SOI存在问题有望得到逐步解决,因此,加大对SOI新技术的研究投入具有非常重要的战略意义。

对于体硅材料及MOSFET的辐射效应目前国内外都已进行了大量研究,但对于SOI的辐射效应研究才刚刚开始。SOI电路结构也在不断发展,除了传统的辐射效应如总剂量效应、单粒子事件和剂量率效应外又出现了一些新的现象,例如multi-bit upset,micro-dose,gate rupture errors 和 micro-latch等。随着SOI技术的发展,迫切需要针对SOI器件和电路因辐射引起的新现象进行研究,这对开发设计新的抗辐射器件与电路也具有重大的意义。