基于DP83640的秒脉冲移相器设计与实现

崔海波,王 康,武建锋

(1.中国科学院国家授时中心,西安 710600;2.中国科学院大学,北京 101408;3.时间基准及应用重点实验室(中国科学院),西安 710600)

0 引言

高精度的时间、频率信号在卫星导航、电力等领域愈发重要,尤其是时间同步技术,其精度往往需要达到纳秒甚至更高。时间同步技术就是使用外部的标准信号来同步本地所产生的信号[1]。原子钟作为提供高精度时间的关键设备,其精度日益增加,为了满足高精度时间同步的需求,相位微跃技术的精度也在不断提高。同时,由于环境变化和器件老化等原因,原子钟不可避免地存在一个长期漂移的变化趋势,导致守时精度恶化,虽然多数情况下引起的漂移量变化都很微小,但是对于高精度时间同步场合却会产生很大的误差。相位微跃技术可在不改变原子钟输出原始信号的前提下,对其频率和相位在一定范围内进行微调输出,消除原子钟输出秒脉冲信号的钟差和钟漂,增加原子钟组的使用寿命,因此相位微跃技术对于原子钟以及时频领域均不可或缺。对于相位微跃技术中的移相部分,相位调整精度直接决定了时间同步系统的同步性能。

目前,数字信号相位调整的主流方法是使用直接数字合成(direct digital frequency synthesis,DDS)技术,通过改变相位控制字和频率控制字的值来实现相位和频率的调整,其调整精度受制于频率和相位控制字位数。单一使用DDS进行秒脉冲相位微跃的最小分辨力仅可达皮秒量级[2],使用DDS和锁相环技术的分辨力也仅达到了6 fs[3]。本文就数字信号相位调整提供了一种新思路,相位调整分辨力可达亚飞秒量级,平均相移准确度也可达0.1 fs。移相精度相对于单一使用DDS技术可大幅提升。

本文主要针对相位精密调整设计了一台高精度可相移的秒脉冲移相器,给出了该秒脉冲移相器的设计方案以及具体的实现原理,包括硬件设计与软件思路,最后给出了平均相移准确度的测试结果。

1 秒脉冲精密移相器的设计和移相原理

1.1 系统设计

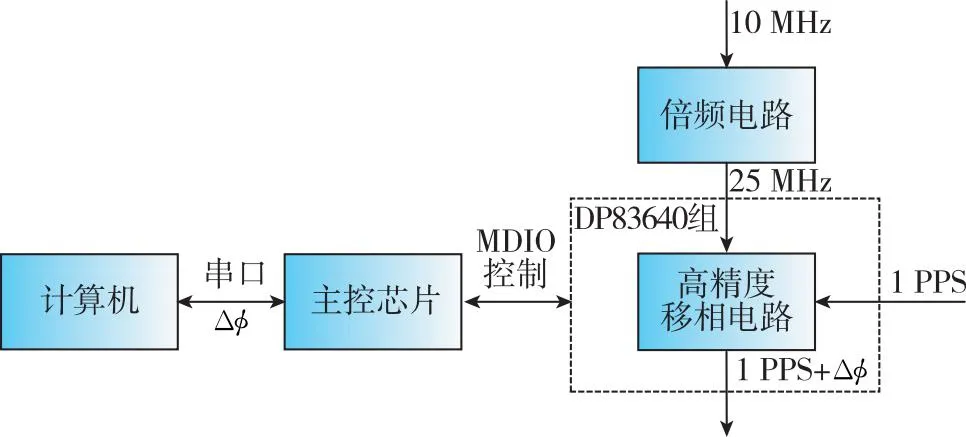

秒脉冲移相器设计如图1所示,其主体部分由倍频电路、主控芯片和移相电路组成。倍频电路将外部输入的10 MHz正弦信号通过锁相环倍频成25 MHz方波作为移相电路的频率源输入。需要移相电路产生的标准秒脉冲(one pulse per second,1 PPS)信号与外部1 PPS信号同步时,主控芯片通过MDIO端口控制移相电路获取外部1 PPS信号到达移相电路的时间,并根据这个时间产生粗同步的1 PPS信号;需要移相电路产生的1 PPS信号进行相移时,计算机通过串口输入相位偏移量Δφ给主控芯片,主控芯片对相位偏移量进行处理,之后通过MDIO端口发送到移相电路进行相移,此时移相电路输出1 PPS+Δφ信号。

图1 秒脉冲移相器系统设计图

1.2 DP83640组的组成

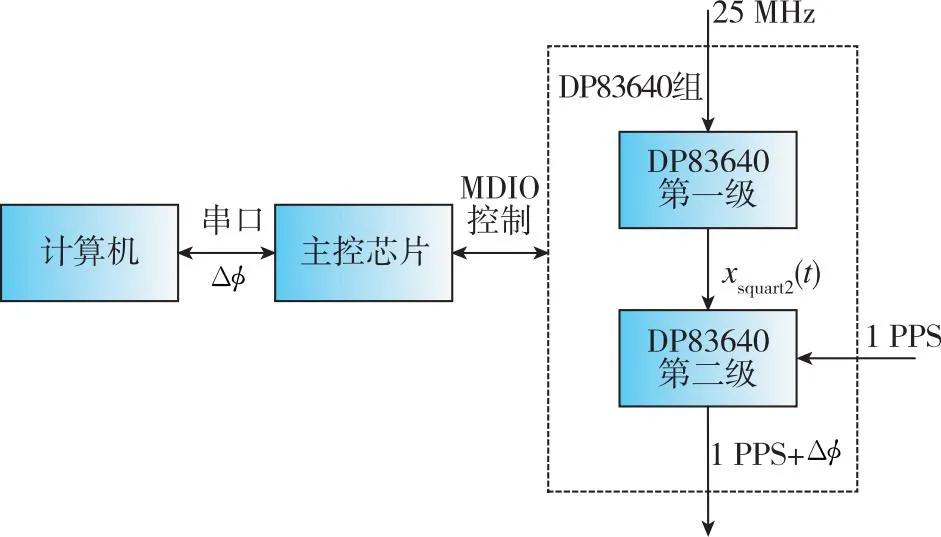

DP83640组由2个DP83640芯片级联组成,如图2所示。单个DP83640芯片接入外部25 MHz也可输出1 PPS信号,但移相范围只能为8 ns的整数倍,即最小移相分辨力仅为8 ns,移相精度较低,不适用于高精度时间同步场合。单个DP83640 芯片能够输出相位可微调的方波信号,微调分辨力远小于8 ns,可作为第二级DP83640的频率源输入,两级DP83640级联可弥补单个DP83640芯片输出的1 PPS信号相移分辨力不能小于8 ns的问题。而两级以上的DP83640芯片进行级联虽也能实现1 PPS 信号的相位微调,但对最小相移分辨力没有提升,反而会增加电路噪声,故采用两级DP83640芯片级联作为精密移相器的核心部分。

图2 DP83640组内部级联图

图2中计算机端输入相位调整量Δφ,通过主控芯片将Δφ拆分为小于8 ns的相位偏移量Δφ1和8 ns 的整数倍偏移量Δφ2分别送入DP83640组的第一级和第二级。设方波信号为

(1)

其中,E为方波的幅值;f为频率。

则第一级DP83640输出的信号为

(2)

其中,f=25 MHz。

第一级DP83640对输出的25 MHz方波进行相位调整量为Δφ1的相位微调,第二级DP83640同时对1 PPS信号进行相位调整量为Δφ2的相位粗调,第二级DP83640即可输出相位调整量为Δφ的1 PPS+Δφ信号,二者相互配合,实现对输出秒脉冲信号的相位调整。

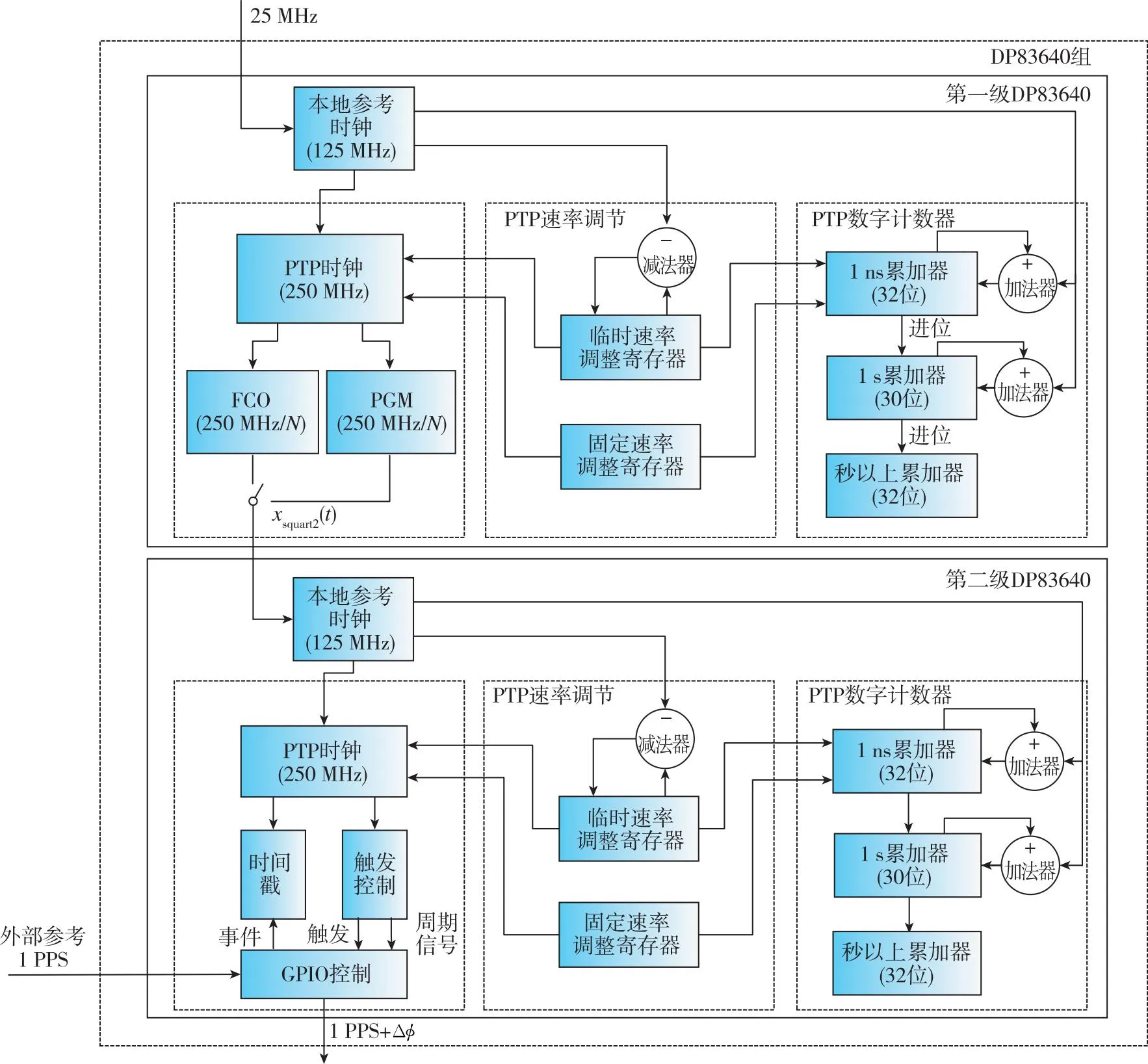

DP83640组由本地参考时钟、精密时间协议(precise time protocol,PTP)时钟、脉冲控制振荡器(frequency-controlled oscillator,FCO)、相位产生模块(phase generation module,PGM)、触发控制模块、时间戳模块、通用输入输出(general purpose input out-put,GPIO)控制模块、PTP速率调整模块和PTP数字计数器组成,如图3所示。

图3 DP83640组内部功能组成图

本地参考时钟同步于外部的25 MHz参考输入,给内部其他模块提供125 MHz的频率源。

PTP时钟是DP83640内部实现移相功能的主要时钟,它同步于外部的125 MHz参考输入,该时钟的运行频率是250 MHz。

PTP速率调节模块主要由临时速率调整寄存器和固定速率调整寄存器组成,通过这两种模块可同步控制PTP时钟和PTP数字计数器。PTP速率调节模块对PTP时钟内部250 MHz信号的控制量可通过PTP数字计数器的数值变化量进行显示,同时也可通过对PTP数字计数器的控制间接控制PTP时钟内部250 MHz频率信号。

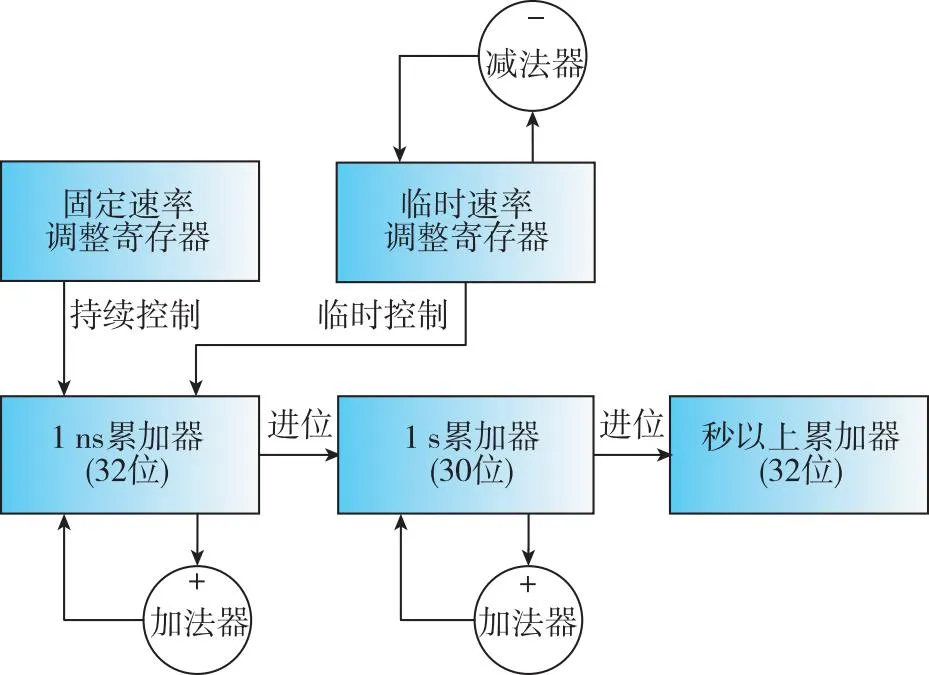

PTP数字计数器主要由3个表示不同时间单位的计数器所构成,主要由32位的秒以上累加器、30位的1 s累加器和32位的1 ns累加器组成[4],如图4所示。

图4 PTP数字计数器原理框图

PTP计数器的值由秒以上累加器和1 s累加器共同表示,当1 ns累加器的值等于232时,向1 s累加器进位,当1 s累加器的值等于109时,向秒以上累加器进位[4]。固定速率调整寄存器可以设置一个值来持续地控制1 ns累加器的数值,纠正1 ns累加器累加到232的时间长度,即可以2-32的最小分辨力来调整1 ns的时间长度;临时速率调整寄存器可以设置一个以8 ns为周期的周期数,在设定时间长度后按照固定速率调整寄存器的值来调整1 ns累加器的数值。

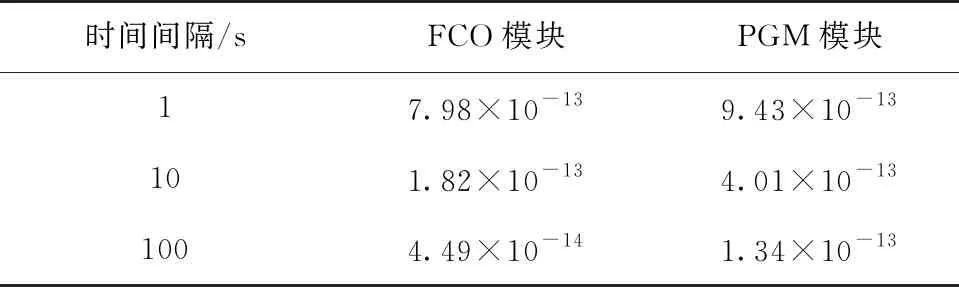

通过配置寄存器可选择频率源是PGM模块还是FCO模块,PGM和FCO均可输出250 MHz/N的方波,其中N为2~255的整数,N的数值也可通过配置寄存器进行配置。两种频率源产生模块各有优劣:FCO模块抖动性能更好,但临时速率调整寄存器可设定的最大调整周期数较小;而选用PGM作为频率源时,临时速率调整寄存器可设定的最大调整周期数虽更大,但抖动性能不如FCO[4]。将第一级DP83640通过FCO模块和PGM模块产生的25 MHz方波信号分别接入到53100A相位噪声分析仪(Allan偏差优于5×10-15/s,相位噪声优于-175 dBc/Hz@10 MHz)进行测量,53100A相位噪声分析仪可以快速准确测量出两种频率源的Allan偏差,主要测量频率源模块的短期频率稳定度,故测量时间设定为30 min,53100A的参考信号选用UTC(NTSC)标准10 MHz信号,测量结果如表1所示。

表1 FCO模块和PGM模块的频率稳定度

由表1可得, FCO模块产生的25 MHz方波信号的短期频率稳定度均更优于PGM模块所产生的25 MHz方波信号,抖动性能与预期结果一致,故选择短期频率稳定度更好的FCO模块作为第二级DP83640的时钟源。

时间戳模块可以对外部输入的参考1 PPS打时间戳,通过触发控制模块和GPIO控制模块可在与外部参考的1 PPS所记录的时间戳相同的纳秒时刻产生1 PPS信号,产生的1 PPS信号与外部参考的1 PPS信号误差在8 ns以内。

1.3 移相模块的移相策略

DP83640内部移相模块总共有4种机制来调整PTP数字计数器的值,分别为直接读写、加减调整、固定速率调整和临时速率调整[5],其中PTP数字计数器的调整量与PTP时钟频率的调整量在采用固定速率调整和临时速率调整这两种方式时相对应。

直接读写调整方式是指将时间值通过对内部寄存器的写入直接设置到1 s累加器和秒以上累加器中,这种方式适合时间偏差较大时使用。例如,当前PTP计数器的值为5 s 3 000 ns,外部输入的时间值为6 s 4 000 ns,写入完成后内部PTP计数器的值将立刻改变为6 s 4 000 ns。

加减调整是指PTP计数器当前的值直接与以纳秒为单位的调整量相加,调整量可正可负,这种方式适合时间偏差大于8 ns时使用。例如,当前PTP计数器的值为5 s 3 000 ns,外部输入的时间值为+200 ns,写入完成后内部PTP计数器的值将改变为5 s 3 200 ns。

固定速率调整方式是通过对1 ns累加器的操作所实现的,1 ns累加器在每个间隔为8 ns的内部时钟周期均加上一个由用户写入DP83640固定速率寄存器的值RATE_TEMP,当1 ns累加器的值溢出时再根据用户设定的调整方向向1 s累加器进行进位或者借位,从而达到调整速率的目的[6]。对DP83640固定速率寄存器和调整方向一旦设置完毕,在每个8 ns 的时钟周期对1 ns累加器的操作均会生效,所以称为固定速率调整,这种调整方式适合时间偏差小于周期间隔时间8 ns时使用。例如,设定固定速率调整至相对于外部参考时钟的+100×10-6:

1)因标称的参考周期为8 ns,一个周期的调整量为

8 ns×10-4=0.000 8 ns

(3)

2)转换为固定速率调整寄存器值为

0.000 8×232≈3.4×106(0x346DC6)

(4)

将0x346DC6写入固定速率寄存器即实现PTP计数器和PTP时钟频率相对外部参考时钟+100×10-6的调整。

临时速率调整同样是通过对1 ns累加器的操作所实现的,与固定速率调整不同的是临时速率的调整是在PTP临时速率延时寄存器所设定的持续时间段内,根据用户所设定的临时速率寄存器的值RATE_TEMP进行调整。在PTP临时速率延时寄存器所设定的持续时间结束后,速率纠正数值将切换回固定速率纠正数值,这种调整方式相位调整精度最小可达到

(5)

适合精细调整时间偏差时使用。例如,在1 ms内临时速率纠正时间为+3 ns。

1)计算出临时速率调整时间

1 ms÷8 ns=125 000时钟周期(0x1E848)

(6)

2)一个周期的调整量为

3 ns÷125 000=0.000 024 ns

(7)

3)转换为固定速率寄存器值为

0.000 024*232≈1.0×105(0x192A7)

(8)

将0x1E848写入临时速率寄存器,同时将0x192A7写入固定速率寄存器,即可在1 ms内临时纠正PTP计数器数值增加3 ns的调整和PTP时钟的相位向正方向移动3 ns的调整。

DP83640组主要通过加减调整和临时速率调整的方式对输出的1 PPS信号进行相位的调整。例如,外部串口输入的Δφ相位偏移量为+21 ns,通过主控芯片分解成Δφ1=5 ns的相位微调量和Δφ2=16 ns的相位粗调量。主控芯片将Δφ1写入第一级DP83640,通过临时速率调整对25 MHz方波信号进行移相,因为FCO临时速率调整的最长持续时间约为500 ms,所以需要临时速率调整的时间不能过长,同时也不能使一个周期调整量很大,故按照临时速率调整量的大小进行时钟周期数的匹配。5 ns的调整量匹配得到临时速率调整时间为100 000个时钟周期(0x186A0),则一个周期的调整量为

5 ns÷100 000=0.000 05 ns

(9)

转化为固定速率寄存器的值为

0.000 05*232≈2.2×104(0x346DC)

(10)

将0x186A0写入临时速率寄存器,同时将0x346DC写入固定速率寄存器,第一级DP83640即可在 0.8 ms内完成25 MHz方波信号的移相;第二级DP83640则采用在当前内部PTP计数器的秒以上累加器加上Δφ2=16 ns的方式进行移相,当检测到当前的秒脉冲信号产生完成,在下一个秒脉冲到来之前,重新按照PTP计数器的时间产生秒脉冲,此时产生的秒脉冲便完成了+21 ns的相位调整。

2 秒脉冲精密移相器的软硬件设计

2.1 硬件设计

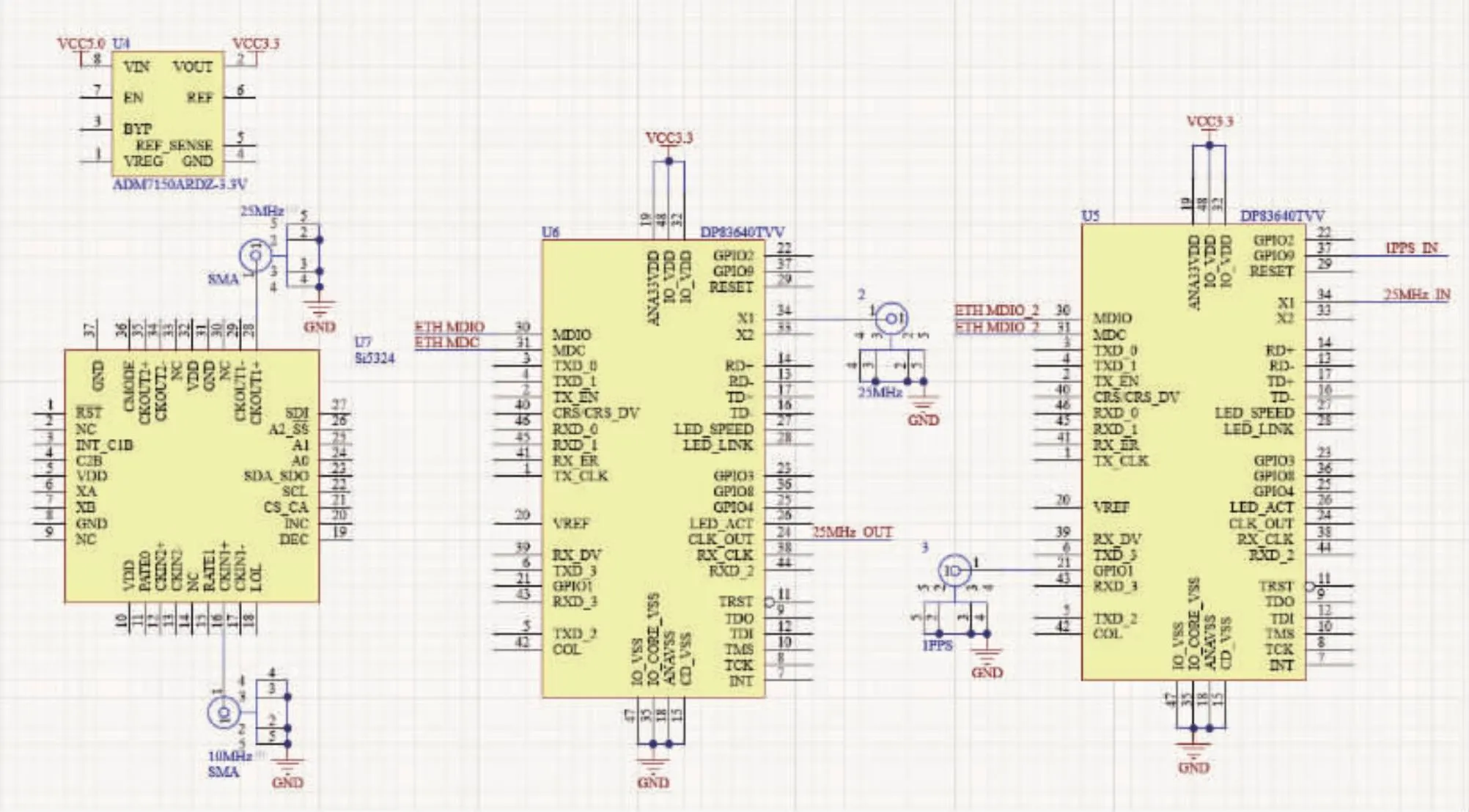

秒脉冲移相器的硬件部分设计主要由主控部分、Si5324倍频电路和DP83640组组成,如图5所示。ADM7150ARDZ-3.3芯片对外部输入的5 V电压进行降压,其具有极低的噪声,电压输入5 V且输入信号频率1 kHz时,电压抑制比大于90 dB,故适合应用于高精度电路,ADM7150ARDZ-3.3芯片为Si5324和DP83640组提供稳定的3.3 V供电。Si5324是Silicon Labs公司的一款任意频率时钟发生芯片,主控芯片利用IIC协议对它进行配置,Si5324的CKIN1+引脚接入外部输入的10 MHz正弦波,从CKOUT1+引脚输出25 MHz方波。

图5 秒脉冲移相器硬件原理图

硬件设计的关键主要为DP83640组的设计,秒脉冲移相器的DP83640组的硬件PCB如图6所示。

DP83640组通过MDIO引脚和MDC引脚与ARM处理器进行通信,第一级DP83640通过X1引脚获取外部Si5324锁定外部10 MHz频率源产生的25 MHz方波,通过CLK_OUT引脚可输出受第一级DP83640控制的25 MHz方波信号作为第二级DP83640的频率源,第二级DP83640再通过CLK_OUT引脚产生一个10 MHz的方波信号。

两级DP83640均选用GPIO9引脚作为外部事件输入引脚,内部寄存器可获取外部的标准秒脉冲的上升沿时间,通过GPIO1引脚在内部寄存器所记录的时刻产生脉冲宽度可调的秒脉冲。

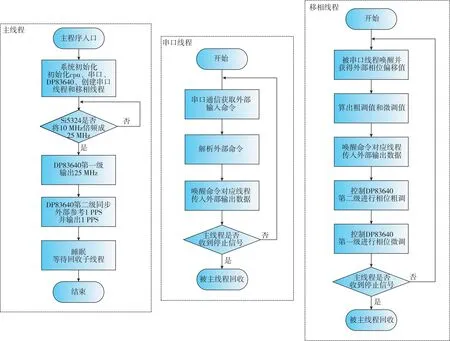

2.2 软件设计

系统软件部分主要分为3个线程的操作,软件流程图如图7所示。开机自动运行主线程,主要包括:进行系统、串口和DP83640组等的初始化。初始化完成后读取Si5324的LOL寄存器位,判断是否已经倍频25 MHz成功,当Si5324成功输出25 MHz后,主控配置DP83640第一级输出25 MHz来驱动第二级DP83640。然后获取外部原子频标输入秒脉冲信号的时间宽度,将误差值写入固定速率调整寄存器,这样确保DP83640内部的PTP精密时钟输出的秒脉冲信号严格为1 Hz。然后获取到外部原子频标输入秒脉冲的时间戳,同时在下一秒相同的纳秒时间戳产生一个秒脉冲信号。此时,DP83640产生的秒脉冲信号与外部原子频标输入秒脉冲的误差应在8 ns内。

图7 软件设计流程框图

主线程创建串口线程和移相线程,串口线程通过串口接收和处理外部计算机端输入的相位偏移值:当串口线程接收到外部计算机端通过串口输入的Δφ相位偏移量的大小和方向时,串口线程将会唤醒睡眠的移相线程并传入移相值Δφ和移相方向。移相线程通过分析处理后先分成8 ns的整数倍和8 ns以下两部分,然后对其进行分别处理。8 ns 的整数倍部分通过直接加减调整的方式进行移相,将DP83640第二级产生秒脉冲信号的时间戳加上相位偏移值,直接通过寄存器写入时间值,以达到更改DP83640第二级产生的秒脉冲信号的纳秒时刻的目的。对于相位偏移值小于8 ns的部分均采用临时速率调整,将此部分相位偏移值分为6个档位,按照这6个档位对相位偏移值进行拆分,将小于8 ns的相位偏移量按照顺序1×100ns、1×10-2ns、1×10-4ns、1×10-6ns、1×10-8ns和1×10-10ns依次取模,所得相位偏移量余数再给下一级进行取模,便将小于8 ns的相位偏移量进行了拆分,以避免FCO频率源的临时速率调整的时间长度不足和减少移相精度的丢失。例如外部串口输入的相位调整量为6.123 456 789 1 ns,按照6个档位可将其相位调整量分解为6×100ns、1.2×10-1ns、3.4×10-3ns、5.6×10-5ns、7.8×10-7ns和9.1×10-9ns,各个档位按分解的相位调整值分别写入DP83640第一级进行临时速率调整,以达到纳秒以下移相的要求。

3 移相测试

3.1 移相理论精度

秒脉冲移相器通过临时速率调整的方式实现秒脉冲信号的最小相移,通过临时速率调整可实现32位的1 ns累加器一个数值的相位移动,即理论可实现秒脉冲最小相移分辨力ΔTmin为

(11)

PTP时钟计数器可通过临时速率调整方式进行多次调整,没有超前或滞后调整的边界。PTP时钟计数器的调整量也与PTP时钟的相位调整量相对应,PTP时钟的相位也可以任意调整。由于PTP时钟相位可任意调整,所以可实现秒脉冲移相器-0.5~+0.5 s范围的相位调整。

3.2 移相测试和结论

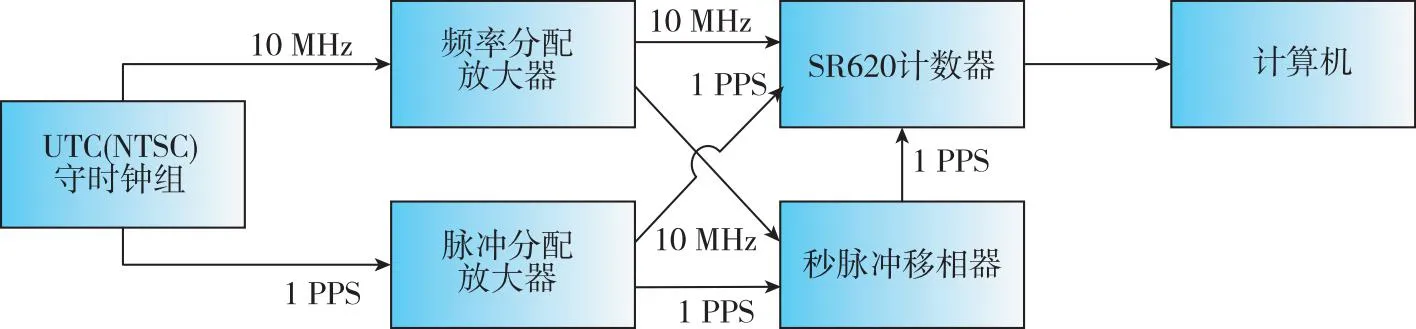

测试平台如图8所示,以UTC(NTSC)守时钟组输出的频率信号作为频率源,频率源输出10 MHz 给频率分配放大器、输出1 PPS外部参考给脉冲分配放大器。频率分配放大器放大分配后一路输出10 MHz给SR620作为外部参考,一路输出给秒脉冲发生器作为频率驱动;脉冲分配放大器输出一路1 PPS给SR620作为开门信号,秒脉冲发生器输出一路1 PPS给SR620作为关门信号。通过计算机软件控制秒脉冲发生器,同时使用计算机采集计数器的测试数据,采集时间间隔设置为1 s,通过Stable32进行汇总分析。

图8 相位微调测试框图

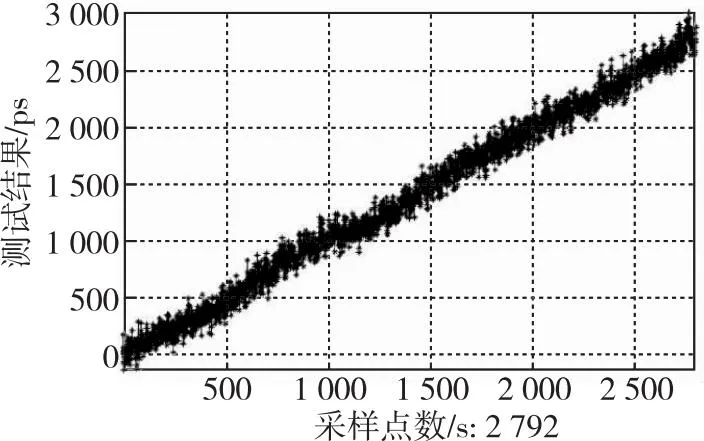

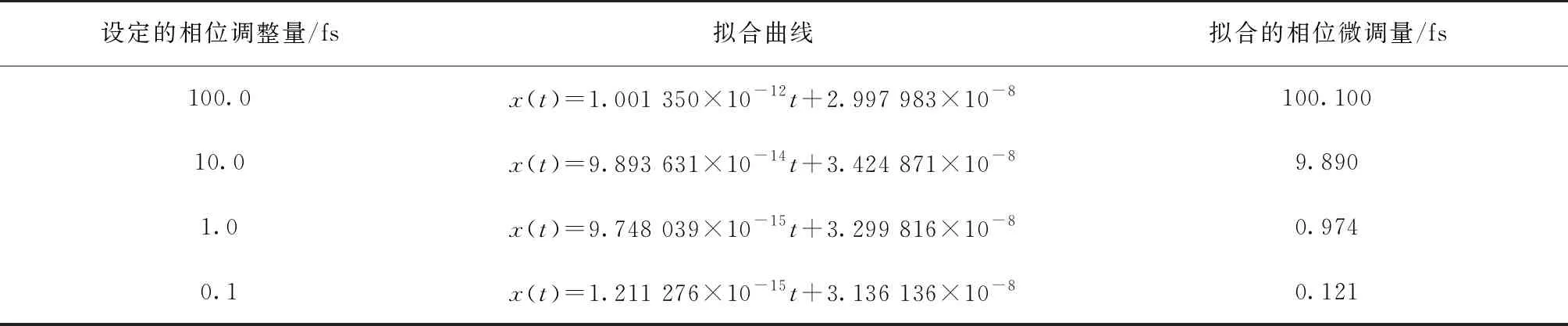

为了验证秒脉冲移相器的最小移相精度,设定相位调整量Δφ分别为100 fs、10 fs、1 fs和0.1 fs,依次进行相移精度测试。SR620最小分辨力为25 ps[7],不能直接测量出相位移动的偏差,故以0.1 s的时间间隔,持续按照不同的Δφ值进行相位步进,连续调整多次,同时用SR620进行数据的采样,对采集到的数据进行线性拟合,计算相位调整的分辨力,测试数据如图9所示。对移相的数据进行线性拟合后,得到的一次函数的斜率为10次移相的斜率,对其乘以0.1便可得到单次相位调整量Δφ。

(a) Δφ=100 fs

图9中,Δφ为100 fs测试了2 792 s,Δφ为10 fs测试了32 000 s,Δφ为1 fs测试了32 729 s,Δφ为0.1 fs测试了49 001 s,对不同的相位调整量采用不同的测试时间,保证所测时间段内能够计算出外部计算机所设定的相位微调量。从图9可以看出,脉冲发生器和标准秒脉冲的相位差随着时间增加与理论分析基本一致。由表2可得,根据采样所得数据计算结果与设定的相位偏移基本吻合,随着最小移相分辨力的降低,移相误差也在增加,误差由秒脉冲发生器的系统底噪和测量设备的噪声综合造成;同时根据表2也可以看出,秒脉冲发生器的平均相位微跃准确度最高为0.1 fs左右,可说明平均相移准确度基本达到了0.1 fs。

表2 相位微调结果

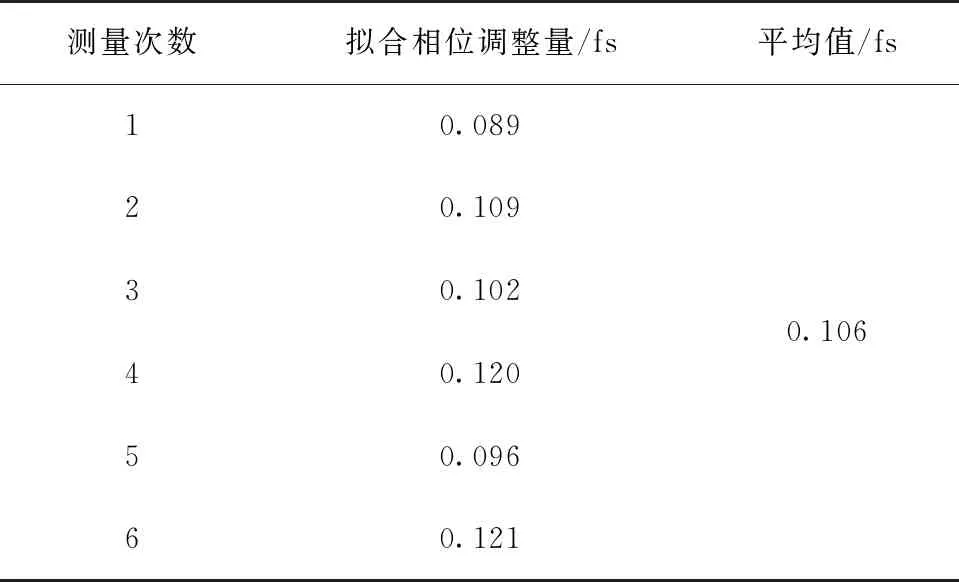

为评估相位调整量Δφ的有效性,对其不确定度进行计算。在同等测试环境设定秒脉冲的相位调整量Δφ为0.1 fs,共进行6次标准化测试,结果如表3所示。

表3 相位调整量为0.1 fs的测试结果

根据不确定度评定方法,计算其拟合相位调整量不确定度u,不确定度u是衡量参数测量结果的精度与稳定性的指标,它表征了测量值的分布概率。根据贝塞尔公式,如式(12)所示,计算实验标准偏差,用平均值实验标准偏差作为该测量结果的重复性,用s(x)进行表示。

(12)

根据计算得出的标准不确定度u可知,由于系统底噪和测量设备的噪声等误差,对其相位调整准确度有一定的干扰,但误差在可接受范围内,所以认为平均相位调整准确度为0.1 fs是有效的。

4 结论

本文通过研究,得到如下结论:

1)提出了一种以DP83640芯片为相位微跃的核心部件的秒脉冲移相器,系统搭建较为简单,秒脉冲移相精度更高,可以补偿原子钟因漂移所引起的守时误差,对于提升守时系统的稳定性具有一定意义,为相位微跃技术提供了一种新思路。

2)受电路噪声的影响,移相测试的实验结果表明秒脉冲移相器的平均相位微调准确度基本可以达到0.1 fs。