基于ATE 的测试向量自动生成技术研究

韦纯进,廖勇,张亭亭,李佳俊

(航天科工防御技术研究试验中心,北京,100854)

0 引言

随着存储器的不断发展,实现存储器全地址多功能测试所需要的向量深度也急剧增加。针对大容量存储器的测试开发,利用传统的手动复制法实现全地址测试向量编写会使软件变得非常卡顿,甚至需要耗费十几个小时才能完成一个完整向量的编写。加之单个存储器需要完成MSCAN、CheckBoard、对角线类、MARCH 等不同算法向量的编写,若全部采用手动复制法编写,会使得开发效率非常低。并且,目前大容量FLASH 的测试时间花费较长,主要因为全地址测试向量编写均采用的是字节写(Word Program)模式,这种存储器数据写入方式的效率较低,进而影响一线测试效率。

因此,研究如何实现存储器的数据快速高效写入对提高存储器的开发和测试效率尤为关键。鉴于此,考虑到基于ATE 的DSRC 技术在向量自动生成方面的便利性以及写缓冲技术在存储器数据快速写入方面的高效性,本文将基于DSRC 技术和写缓冲技术,实现存储器全地址测试向量自动生成以及测试数据的快速写入,并以MT28EW01GABA1HPC 为例,对测试开发效率及测试效率的提升情况进行对比。

1 MT28EW01GABA1HPC 芯片概述

MT28EW01GABA1HPC 是Micron 公司生产的容量为1Gbit 的16 位NorFlash 存储器,供电电压为2.7V ~3.6V。该存储器芯片典型的单字写入时间25μs,片擦除时间208s,512 字写缓冲时间1μs。芯片引脚定义如图1 所示。

图1 MT28EW01GABA1HPC引脚图

(1)地址线:A0~A25;

(2)数据线:DQ0~DQ15;

(3)控制信号:WE#、RST#、OE#、CE#、BYTE#、VPP/WP#;

(4)准备/忙状态标志位:RY/BY#。

2 基于DSRC 的存储器测试向量生成

■2.1 DSRC 向量自动生成

DSRC(Digital Source Setup:数据源设置)技术是ATE 测试系统自带的数据源设置工具,可以极大地提高存储器测试向量编写的效率,本文通过DSRC 完成地址向量的自动生成。但是DSRC 生成的测试向量的深度受限于ATE的License,可选的深度有1M、2M、8M、16M 不等,当存储器的容量超过DSRC 所支持的地址范围时,则需要通过底层代码去遍历存储器高位地址,以实现全地址测试。MT28EW01GABA1HPC 的地址引脚范围为A0~A25,如果ATE 只能生成2M 存储深度的DSRC,覆盖的地址范围为A0~A20;则存储器高位地址A21~A25 只能通过底层测试算法去遍历。本文采用的是页缓冲快速写入,一次页缓冲可写入512 个Word,因此生成的地址范围为A08~A0,基于DSRC 的测试向量生成步骤如图2 所示。

图2 基于DSRC 测试向量生成步骤示意图

由图2 可知,就要DSRC 的测试向量生成主要分为三步:

第一步:设置PORT。在Pin Configuration 中设置相应的端口Port_A08_A0(A0~A08),由于DSRC 的存储向量深度为2M,因此可覆盖的地址引脚为A0~A08;

第二步:生成DSRC。根据所设置的PORT 端口生成DSRC,首先在向量中右键New Setup 进入到DSRC 界面,然后根据相关需求配置Port 端口、帧数、偏移、DSRC 类型、Option、变量名、映射关系等参数;

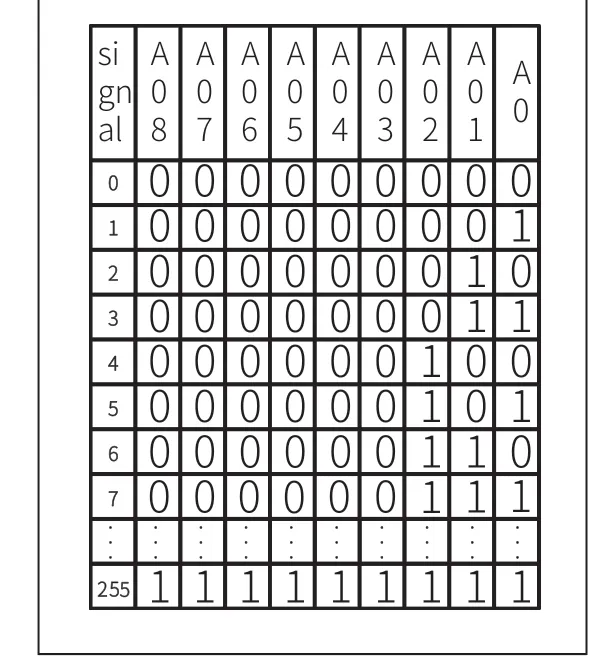

第三步:数据填充。在信号分析器界面对第二步生成的DSRC 进行数据填充。首先在tool 中根据测试向量特征生成特定波形,本文生成的是斜率为1 的直线,x 的取值范围根据设置port 端口而定,此处为0~511。然后在action 中将波形数据下载到生成的DSRC 向量中。通过DSRC 生成的自增地址向量A08~A0 如图3 所示。

图3 基于DSRC 自动生成的地址向量

■2.2 高位地址遍历

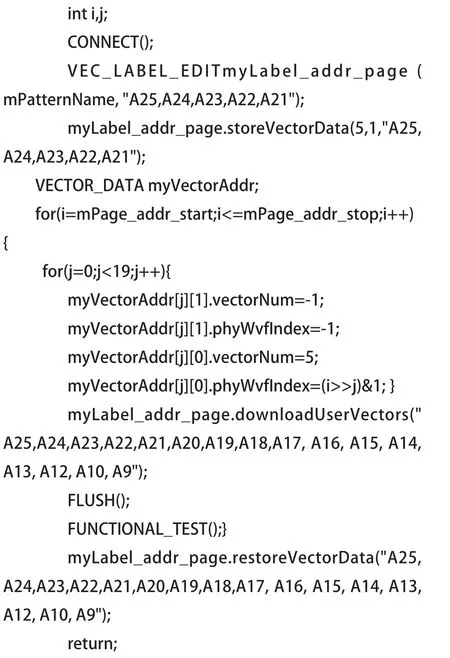

由于2M 的DSRC 生成的地址向量覆盖范围为A20~A0,因此高位地址A25~A21 的覆盖需要通过底层算法去实现,实现过程如图4 所示。即借助于ATE 测试系统的开发环境,通过C++语言实现自定义测试方法,通过编译后,可在流程图界面的测试项中加载该自定义函数,具有较强的灵活性。

图4 底层算法遍历高位地址实现过程

通过底层算法实现高位地址遍历的具体过程如下:

第一步:切换显示类型,进入到ATE 测试系统的底层开发环境,并新建工程,后续在Testflow 中的方法引用则是通过该工程名进行索引的;

第二步:一个工程中可以新建多个方法,在新建方法过程中会提示添加变量,此变量根据测试需求而定,本文添加了两个变量page_addr_start(起始页地址)和page_addr_stop(结束页地址);

第三步:在virtual void run()函数中实现算法。

3 基于写缓冲的存储器测试

■3.1 写缓冲技术

存储器编程有字节写(Word Program)和写缓冲(Buffer Program)两种方式。字节写模式需要4 个周期完成一个Word 的写入,其命令为555,AA;2AA,55;555,A0;PA,PD;该芯片写入单个Word 需要25us 左右,编程效率极低。该芯片在写缓冲模式则只需要517 个周期(包括指令周期和数据写入周期)即可完成最多512Word的写入。其命令为555,AA;2AA,55;BAd,25;BAd,N;PA,PD;BAd,29;一次写缓冲需要200μs 左右,经对比,通过写缓冲模式进行编程可以极大提高存储器测试效率。

■3.2 存储器测试常用算法

存储器的故障检测是基于特定的测试图形算法实现的。针对存储器的故障测试,一个高效、可靠的测试算法需要尽可能少的测试时间,覆盖更多的故障类型。以下是几种经典的存储器故障测试算法。

3.2.1 MSCAN 算法

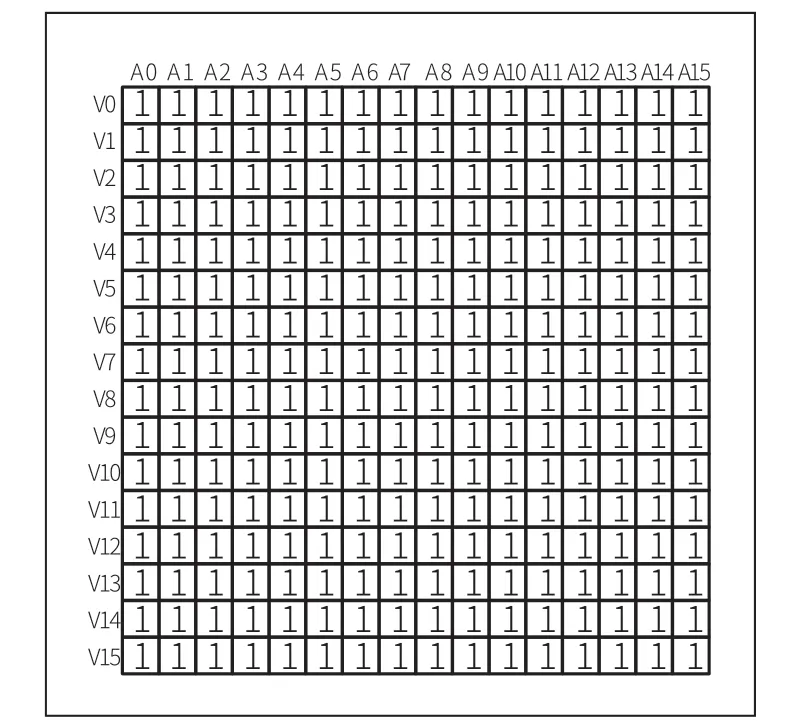

MSCAN 算法是存储器最基础的一种测试算法,是对所有存储单元进行逐一扫描并统一写入逻辑0 或逻辑1,也称为全0/全1 算法。具体实现步骤为:对所有存储单元写入0 或者全1(NorFlash 通过擦除写入逻辑1),然后再读取所有存储单元进行比较,检查是否存在错误。全0/全1 算法测试图形如图5、图6 所示。

图5 MSCAN 全0 算法

图6 MSCAN 全1 算法

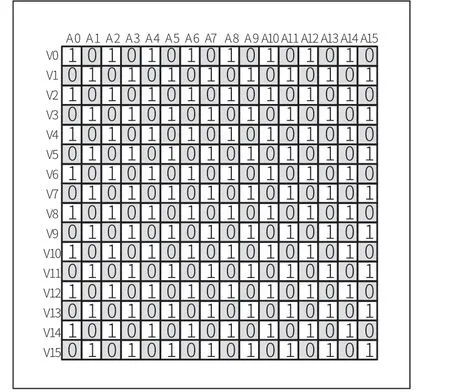

3.2.2 Checkboard 算法

Checkboard 算法是将逻辑0 和逻辑1 奇偶相间地写入存储单元,形成类似于棋盘的格式,Anti-Checkboard 算法则与之相反,将逻辑1 和逻辑0 奇偶相间地写入存储单元,这两种算法也称为奇偶校验法。Checkboard 算法和Anti-Checkboard 算法的测试图形如图7、图8 所示。

图7 棋盘算法测试图形

图8 反棋盘算法测试图形

3.2.3 对角线算法

对角线算法将整个存储单元视为一个存储阵列,对于处于存储阵列对角线位置的存储单元写入逻辑值的同时,使其他存储单元保持初值或写入不同的逻辑值。图9 为对角线算法的测试图形。

图9 对角线算法测试图形

■ 3.3 基于DSRC 和写缓冲的全0 测试向量自动生成

本小节基于DSRC 技术和写缓冲技术开展了芯片的全0 测试向量编写。图10 为基于DSRC 技术的写缓冲向量图形,第0、1 行向量为芯片上电复位后等待进入工作状态,第3~6 行向量为写缓冲指令,使芯片进入写缓冲状态,第8 行向量则通过SSRC 指令调用前述基于DSRC 生成的地址向量,第9~11 行向量则为通过512 次LOOP 循环指令向芯片内写入全0 数据,该芯片一次写缓冲最大可写入512 个Word,第12 行向量为确认写缓冲指令。第12 行向量则通过RPTV 循环指令等待写缓冲完成,该芯片一次512Word 的写缓冲典型时间为512μs,选择的芯片工作频率为1MHz,因此循环了512 次。图中第6 行、第8行、第11 行向量中的“.”表示该行向量地址A25~A09 的值与前一行对应的值保持一致,需提前在Timing 文件的Waveform 中进行定义。第9 行中A08~A00 的“...”表示调用通过DSRC 生成的地址向量值,SSRC 和SRCV 指令需成对使用才能完成调用,“SRCV 1 1”表示一次只执行一行DSRC 向量。图中第5 行红色部分A25~A09 的地址向量值是通过底层算法去完成遍历的。

图10 基于DSRC 的底层写缓冲向量

4 结果比对

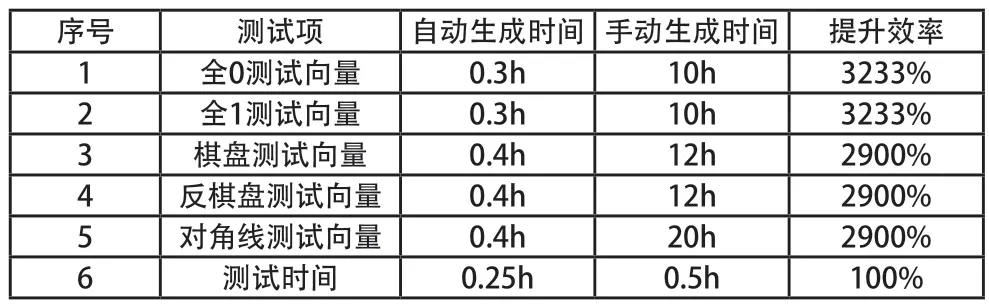

针对MT28EW01GABA1HPC 这款芯片,若通过手动完成全0 测试向量的编写则需要复制2.68 亿行向量,在计算机性能满足要求的前提下,需要复制将近10h 才能完成。若基于DSRC 技术和底层写缓冲技术实现自动向量生成,则只需要编写如图10 所示的一个循环向量(共计约13 行)以及通过DSRC 自动生成一个如图3 所示的A08~A0 的页内地址向量(共计约512 行),然后通过底层算法去遍历高位页地址(A25~A09)即可。经过实际测试,采用该方法完成全0 向量测试只需要约0.3h(包括循环向量编写时间和底层算法编写时间),提升向量开发效率约3233%,具体效率提升情况还受开发人员熟练程度的影响。通过自动生成和手动复制完成向量编写所需的开发时间以及写缓冲与字节写的测试时间对比如表1 所示。

表1 时间效率对比